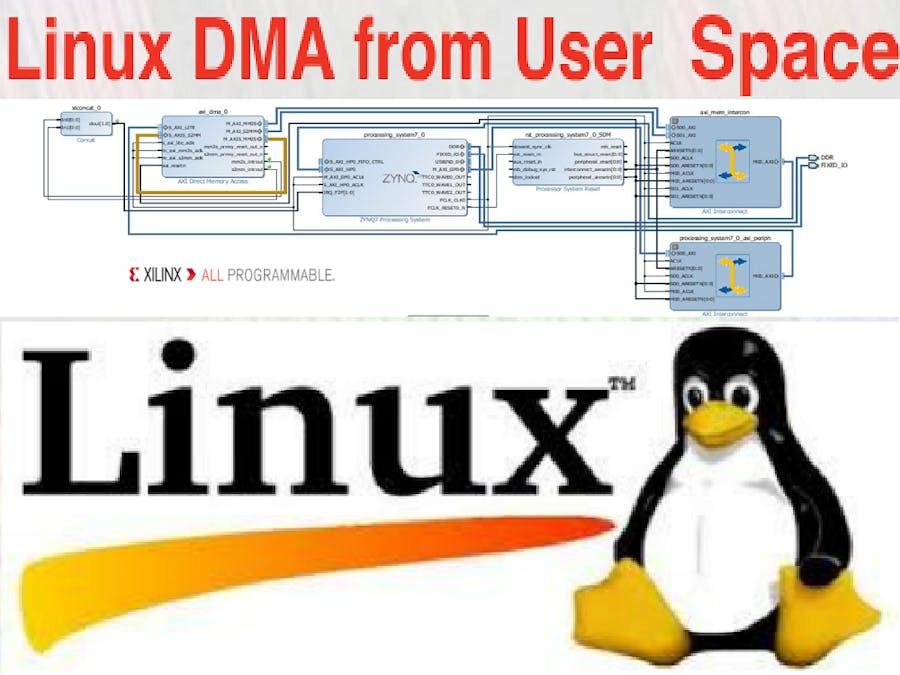

I’ve started with new RTL project for MicroZed 7010 board presetting, added Zynq PS, AXI DMA and FIFO similar to the design in the Introduction to Using AXI DMA in Embedded Linux project (apparently the project is an extension of the refenced one, focused on AXI DMA interrupts), Vivado design can be found uploaded.

note:Please notice the AXI DMA interrupts lines marked for “Debug” and 2 System ILAs added by “Connection Automation” to the lines

SYNTHESIS -> Open Synthesized Design ->Set Up Debug, enable “Trigger Setup”

Generate Bitstream and File -> Export -> Export Hardware to create XSA file (including bitstream)

Design verification with baremetal application (optional)Create Platform Project in Vitis and “import” axi_dma driver example xaxidma_example_simple_intr.c for simple interrupts. The procedure is pretty similar to the described in the https://ohwr.org/project/soc-course/wikis/Standalone-Peripheral-Drivers, but with the Unified Vitis GUI.

note:Please notice lines 331-314 and 404-405 added to the example to generate the transactions/interrupts once per second in infinite loop

MicroZed is connected with uUSB UART and USB JTAG II to my PC, and I've started SystemProject debugging in Vitis

Resume/Continue the debugging in Vitis

In Vivado open HWmanager, auto-connect and program device with bitstream, and “Run trigger” in u_ila_0

note:Please notice Trigger Setup hw_ila_3 conditions “*introut == 1”, it has to beset manually

Linux projectPetalinux setup is pretty similar to the Introduction to Using AXI DMA in Embedded Linux besides the following detail in the https://docs.xilinx.com/r/en-US/pg021_axi_dma/Programming-Sequence

In practice the following code correction worked for me

besides that, in the attached code I use pthread to handle the UIO interrupt with "blocking read", it requires libpthread to be added to petalinux filesystem

Application can be created with the following commands, after that project-spec/meta-user/recipes-apps/dmatest/files/dmatest.c can be replaced with the attached version of the file

petalinux-config --get-hw-description=../mz7010_axi_dma/mz7010_axi_dma.xsa

petalinux-create -t apps --template c --name dmatest --enableIf you create your project with petalinux BSP for Avnet board, like

source /tools/Xilinx/Vitis/2021.1/settings64.sh

petalinux-create -t project -n mz7010_dma_202 -s ./mz7010_som_base_2020_2.bspproject build instruction will look like

petalinux-build -c avnet-image-fullBOOT.BIN can be prepared with

petalinux-package --boot --fsbl ./images/linux/zynq_fsbl.elf --fpga ./images/linux/system.bit --u-boot --forceand if you'd like to review AXI DMA "dma@40400000" node in linux device tree, the following conversion of the system.dtb into ASCII form can be handy

dtc -I dtb -O dts images/linux/system.dtb -o system.dtsFinally, the interrupt can be observed in Vivado HW Manager and in the linux (ID 29+32=61)

Please find attached the application and Device tree correction file associating the AXI DMA node with UIO driver

note: UIO driver can handle only one interrupt per device tree node, apparently it picks up the 1st one in the interrupts list, in our case 29 (it appears as 29+32=61 in the /proc/interrupts)

note: Sometimes Vivado HW manager doesn't recognize ILAs probes in bitstream loaded by FSBL, and reloading the bitstream from the HW manager (after linux boot) fixes the situation. The application initializes AXI DMA node registers, therefore it's alright to reload the bitstream and (re)start the application anytime

Comments