Harris Corner Detector (HCD) is a technique to extract features of corners in the image. (for more info, refer to background.md)In this project, we implement HCD using Xilinx Vitis HLS. The hardware design can be deployed to PYNQ-Z2 borad. The objectives of our implementation are low latency and high throughput, thus we explore some optimization methods for further acceleration of the process.

Major FeaturesThe following list the features of this project, refer to optimization.md for more infomation.

- Hardware implementation of image processing algorithm (HCD) using Xilinx Vivado HLS

- Using several HLS pragma (dataflow, pipeline) to enhance the overall performance

- Parallel processing: Use vector type of PE level parallelism like SIMD to increase HCD throughput

- m_axi interface: Efficient use of memory - packed 24-bit datatype in memory

For more detailed info, please refer to https://github.com/yqchenee/Harris-Corner-Detector-in-PYNQ

HLS synthesis (Vitis tool)- Clone this project, and import kernel code to Vivado HLS (version 2020.2), generate a IP called HCD.

CLI example for running opt4, it can be changed to optx (x = 1~5).

git clone https://github.com/yqchenee/ACA_21S_final.git

vitis_hls -f build/script_opt4.tcl- Import HCD IP to Vivado, then add one DMA (for read and for write), after run auto connection, the block diagram should like following figure.

- Generate bitstream from Vivado GUI or tcl file in build folder, then test your bitstream in pynq.

- Upload src/host folder to pynq's jupyter, then put data/host_test folder to the same folder.

- Upload your bitstream and hardware file.

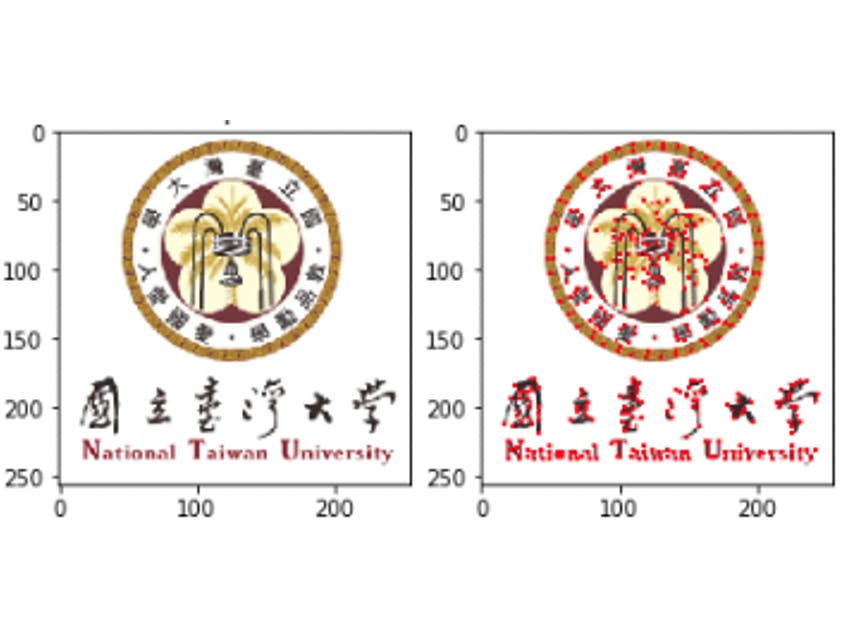

- Execute HCDhost.ipynb in jupyter notebook, following is the figure after correctly execute it.

Comments