ON/OFF temperature control simulation in the Qspice simulator from Qorvo with aVishay NTC thermistor and a small VERILOG module.

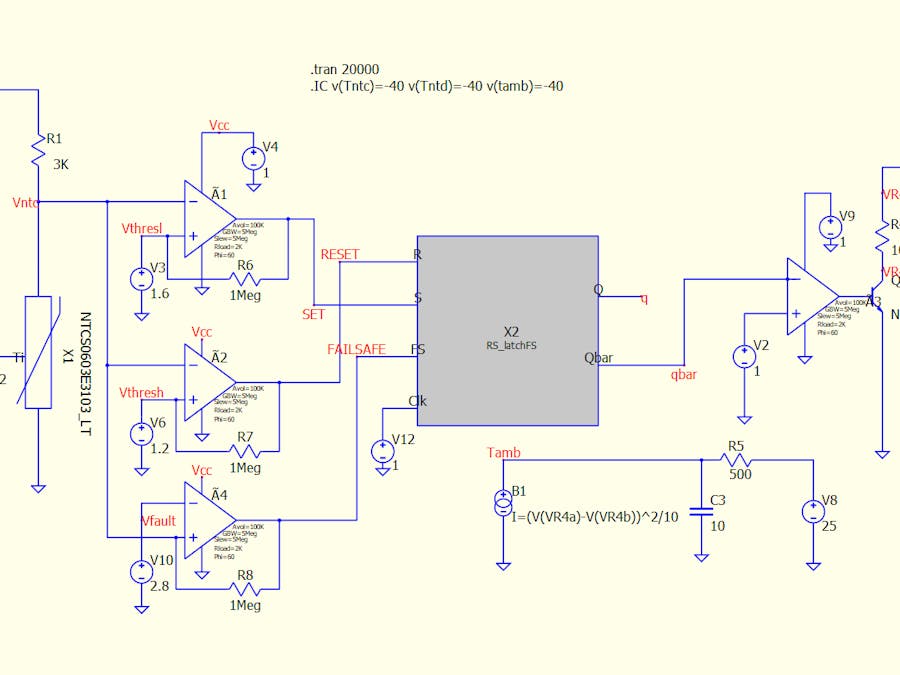

The Qspice simulator from Qorvo is supporting Verilog and C++. Thus the digital part of the simulation has been encoded in VERILOG (basically a RS flip flop with an addition of a fail safe detection in the case the NTC thermistor would go in open circuit)

The SPICE model for the NTC thermistor (Vishay NTCS0603E3103FLT) is not much different than the one used for the LTspice simulations (available on Hackster.io). It has been imported in Qspice with its slightly different specificities.

Here are the simulation results.

The temperature starts up at -40°C with an ambient temperature of 25°C. At this temperature, the fail sage voltage is reached and thus the heater does not work. When the natural warming brings the NTc voltage under the fail safe voltage, the heating works and the limit cycle is maintained.

Comments