The design of a high-speed analog-to-digital converter (ADC) system with a high input frequency (IF) has always proven to be a challenging task. The use of transformers makes this task more difficult because transformers are inherently non-linear, and these non-linear characteristics can make performance difficult to meet standards. This article classifies and explains the issues that should be paid attention to when high-speed sub-ranging ADCs use transformer-coupled front-end designs.

Design ParametersSeveral important parameters need to be considered when designing the front end.

The input impedance is the characteristic impedance of the design. In most cases, its value is 50Ω, but some designs also require other impedance values. Transformers are essentially trans-impedance devices because when necessary, they can also achieve coupling between circuits with different characteristic impedances so that the total system load can be fully balanced.

Bandwidth refers to the range of frequencies used by the system. This width can be narrow or wide, distributed on the baseband (Nyquist frequency), or covering multiple Nyquist zones.

The input drive level is a function of the bandwidth parameter, which sets the system gain required for a particular application. The drive level depends to a large extent on the front-end components used, such as filters and transformers. This requirement may become one of the difficult to achieve parameters.

The voltage standing wave ratio (VSWR) measures the amount of power reflected into the load over the bandwidth of interest. This parameter sets the input drive level required to realize the full-scale input of the ADC.

Passband flatness is the size of performance fluctuations within a specified bandwidth. This may be due to ripple effects or the very slow roll-off characteristics of a simple low-pass filter. The passband flatness is often less than or equal to 1dB, which is critical for the overall system setting.

The signal-to-noise ratio (SNR) is the relative relationship between the signal seen by the converter and its noise. In the front end, SNR may deteriorate due to bandwidth, signal quality (jitter), and gain. Remember, when the signal is amplified, the noise component is also amplified at the same time.

Spurious Free Dynamic Range (SFDR) is the ratio of the full-scale RMS value to the RMS value of the peak spurious spectral component. This is mainly caused by two characteristics of the front end. One characteristic is the linearity or balance quality of the transformer. The latter is related to the second harmonic distortion; the second characteristic is the matching relationship between the gain and the input. As the amount of gain required increases, matching becomes more and more difficult, while the parasitic component of the non-linear transformer (usually regarded as a kind of third harmonic) will increase.

Transformer ParametersThe transformer can be simply regarded as a kind of bandpass filter.

Insertion loss, which represents the loss of the transformer at a specific frequency, is a common measurement index parameter in the datasheet of a transformer, but it should not be an index considered in the design.

Return loss refers to the transformer seen on the primary side when the second terminal of the transformer is connected. For example, when an ideal 1:2 impedance converter has a 100Ω impedance at the secondary end, the impedance reflected in the primary stage is 50Ω. However, this is not always true, because the impedance reflected by the primary side will vary with frequency. As the impedance ratio increases, the return loss will also change accordingly.

Amplitude and phase imbalance is a key performance characteristic of investigating transformer. When the design needs to use an IF frequency above 100MHz, these two specifications can let the designer know how much nonlinearity may be encountered. As the frequency increases, the non-linearity of the transformer also increases. The unbalance of the phase is often the main unbalance, and accordingly, it will bring even-order distortion or increase of the second harmonic.

ADC ParametersADCs can be divided into two types: buffered and unbuffered. The power consumption of unbuffered ADCs is often much greater than that of buffered ADCs, but buffered ADCs are easier to drive.

A switched-capacitor ADC is a specific example of an unbuffered ADC. The front-end design is directly connected to the sample-and-hold circuit (SAH) network inside the ADC. This brings about two problems: one is that the input impedance of the ADC will change with time and mode; the second is charge injection, which will be reflected on the analog input of the ADC, which will bring a filter The problem of filter settling.

It is convenient to understand and use the ADC with buffer. By adopting an isolation buffer that can suppress spikes caused by charge injection, switching transients can be significantly reduced. Unlike the situation in switched-capacitor ADCs, the input termination characteristics will not change with the analog input frequency in the entire specified ADC bandwidth, and the selection of the appropriate drive circuit will become more convenient. The disadvantage of a buffered input stage is that it will make the ADC consume more power.

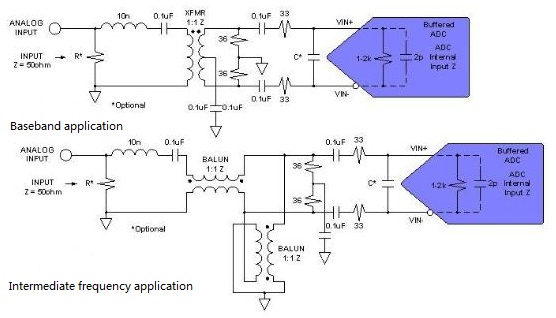

Design ExampleThe design examples for baseband and IF applications are given below, as shown in Figures 1 and 2, respectively.

In baseband applications, the input impedance of ADCs is generally very high, so the importance of input matching is lower and easier to implement. Often one or two small-value series resistors used to attenuate the charge injection effect plus a simple differential input capacitor are sufficient. In this way, only a simple filter is needed to attenuate the broadband noise to obtain the performance.

High-frequency applications require designers to think more. To optimize the matching of the input, it is necessary to match the impedance of the front-end tracking mode to make the input impedance as resistive as possible. Using series or parallel inductors or ferrite beads (shown in the figure is the former), you can eliminate the "capacitance" term.

In short, matching the input can give good bandwidth, gain flatness (smaller changes in power drive) and better performance (SFDR).

The baseband application of a buffered ADC also uses a simple network, similar to the configuration of a switched capacitor ADC. Note that the secondary side should be terminated to match the input of the primary side.

In Figure 2, dual balun (balanced/unbalanced conversion) is used for high IF applications. This allows the input to be well balanced in the range of up to 300MHz so that the second-order distortion is consistent.

SummaryA variety of parameters must be considered in the design to achieve performance. Transformers vary greatly. If the designer can understand the specific transformer performance parameters and consult the manufacturer for the parameters that are not given, he can better predict the characteristics of his design. High IF designs are sensitive to the phase unbalance of the transformer; therefore these designs may require two transformers or balun.

It is also important to know whether the ADC used is buffered or unbuffered. The input impedance of the unbuffered ADC changes with time and the corresponding design is more difficult in the case of high IF.

To optimize the design, the input should achieve tracking matching. Use magnetic beads or low-Q inductors to eliminate the input capacitance component of the switched capacitor ADC. This can maximize the input bandwidth, achieve more optimized input matching, and maintain SFDR performance.

The design of buffered ADCs is more convenient, even at high IF, but they consume more power. No matter what ADC type is used, the design work for baseband applications is simple.

(At last, I'd like to thank Apogeewebfor giving me inspiration. Especially the article about the Analog to Digital Converters)

_adc_OU4HVGTtYn.jpg)

Comments