We propose to implement high compression ratio lossless medical image compression algorithm that is based on gated linear network (GLN), in order to increase efficiency of medical image storage and distribution systems. In comparison with "traditional" context-based data compression algorithms, GLN-based system uses the set of different context models instead of one context model. Outputs of all context models are combined by GLN into the single value of probability that is used as input value for entropy coding algorithm. This idea was introduced by Matt Mahoney, who initiated the development of PAQ archiver series. PAQ archivers have been ranked among the top over several benchmarks measuring compression ratio of lossless compression algorithms.

Empirical success of PAQ archiver series has been explained by research scientist Joel Veness (Google DeepMind). Joel Veness introduced and described architecture of GLN and noted that PAQ algorithm is special case of this framework.

To the best of our knowledge, the implementations of GLN-based compression algorithms in embedded systems have not been presented in literature and in any commercial systems. The advantage of GLN-based compression systems in comparison with "traditional" lossless image compressions algorithms suchs as JPEG-LS and JPEG-2000 is the improved compression ratio. Compression ratio for GLN-based compression system might be at least 20% higher. Therefore, amount of medical images stored in a certain storage theoretically might be increased by 20%. The challenge is the implementation of GLN-based compression with througput that is suitable for practical system.

More in-depth description about GLN's is available in following sources:

1) https://arxiv.org/abs/1712.01897; 2) https://arxiv.org/abs/2002.11611; 3) https://ieeexplore.ieee.org/abstract/document/9134252

More in-depth description about PAQ series is available in following sources:

1) http://mattmahoney.net/dc/dce.html; 2) https://arxiv.org/abs/1108.3298;

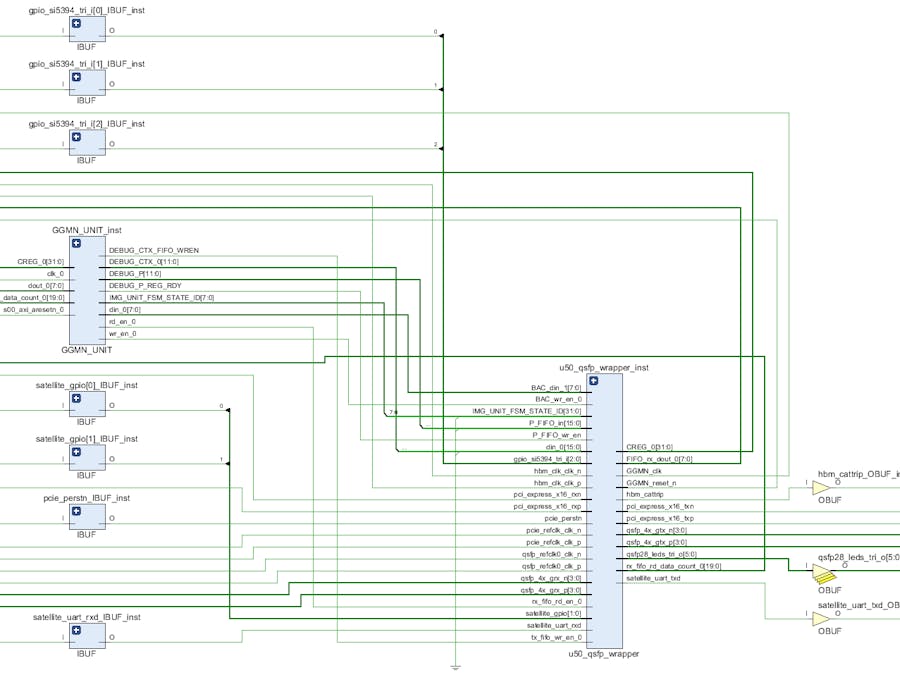

In following figure, dataflow of image compression/decompression is avalaible.

Unfortunately, the project is under development. Nevertheless, it provides the basis for the development of a medical image compression system. A 32-bit input GLN is currently available that can partly provide image compression (some output values are different from those that are produced by software reference implementation). Unfortunately, in order to perform image decompression, the binary arithmetic decoding module has to be implemented.

After the contest, we are going to finish this project, in order to give a solid basais of GLN implemenation in FPGA for Hackster.io community.

Set it up and launchWithin the following steps, it is described, how to launch current implementation of project.

Step #1 - set up the Alveo U50 cardAccording to Alveo U50 Data Center Accelerator Card Installation Guide, set up Alveo U50 Card on PC with Ubuntu OS

Step #2 - launch reference designSince this project is developed on the basis Alveo U50 GT Reference Design for Vivado, we suggest to launch reference desing before implementation of this project. Reference desing files and instructions you can download from Xilinx after registration (https://www.xilinx.com/member/alveo-vivado/u50/Alveo_U50_GT_RefDesign_UserGuide_20201019.pdf). Set devmem2, in order to peek and poke registers of Alveo U50.

Step #3 - download and set python scriptIt is quite convenient to communicate with Alveo50 board via Python scripts. Thus you can easily transfer images to Alveo U50 registers and vice versa. Download Python script and test image that is attached to this project.

Step #4 - implement designDownload zipped Vivado project files. Unzip and compile. Program this to project to Alveo U50 board via programming cable. Turn-off PC and disconnect the programming cable. Turn on PC and launch the Python script.

Comments

Please log in or sign up to comment.