This Project is for beginners to study Verilog HDL and FPGA.

I made some lecture materials using this project for Korean students and I uploaded my youtube. (only Korean... LoL..)

Please Enjoy it!

Matbi Watch Top (Core)Matbi watch top is to make sec, min, hour values every cycle when enable signal is high.

1. "Matbi one sec gen" is to count cycle and generate one sec tick. (tick : one cycle)

2. Using the signal of "one sec tick", It can be generate sec, min and hour values.

Micro Architecture:

Port list:

I connected controller (myip_v1_0.v) to control matbi_watch_top and check time results. I used I/F AXI4-Lite and basic signals such as clock, reset, enable.

"Enable signal" is input, I have a plan to connect switch on zybo Z7.

The matbi watch only runs when the switch is turned on.

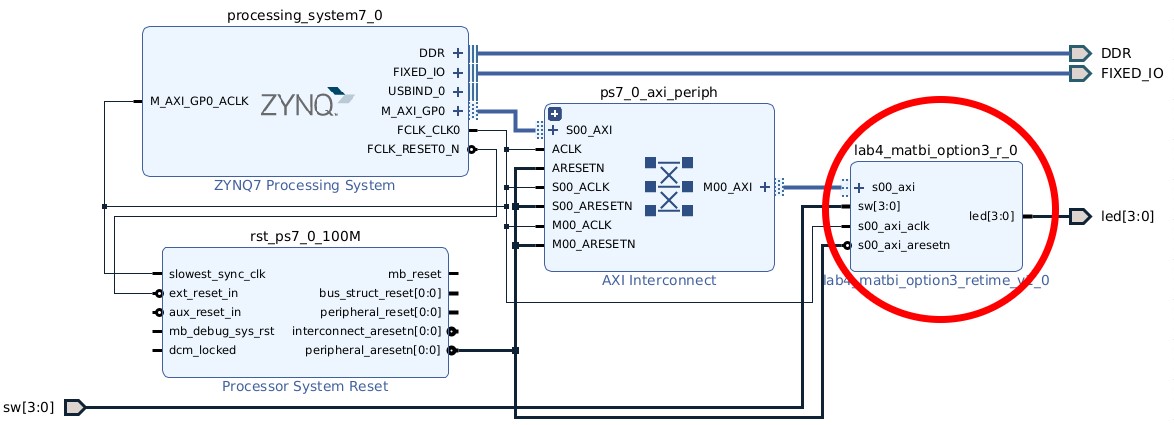

Block diagram is so simple. You can follow up to make this system.

1. Call IP top and PS

2. Change Frequency 100MHz, it is possible to synthesis design on Zybo Z7-20.

3. Click the "auto connection"

Register table is here. You can also easily program SW code.

Making watch using Verilog HDL and FPGA is so useful project to study that how to implement and run FPGA. As you know that, this project is simple but I believe that you can get a lot of experience and grow up your skills. If you can add or modify your own feature in this project, it is meaningful job. Try it!!

Thank you so much to read this article. Have a nice day :)

Comments

Please log in or sign up to comment.