Steve Markgraf's "hsdaoh" Taps Low-Cost HDMI Capture Dongles for High-Speed Data Acquisition

By encoding data as video stripes, this clever project turns cheap HDMI capture cards into high-speed USB 3.0 data acquisition devices.

Developer Steve Markgraf has come up with a smart way to add a high-speed data port to external hardware, by making unusual use of low-cost HDMI capture dongles and cheap field-programmable gate arrays (FPGAs).

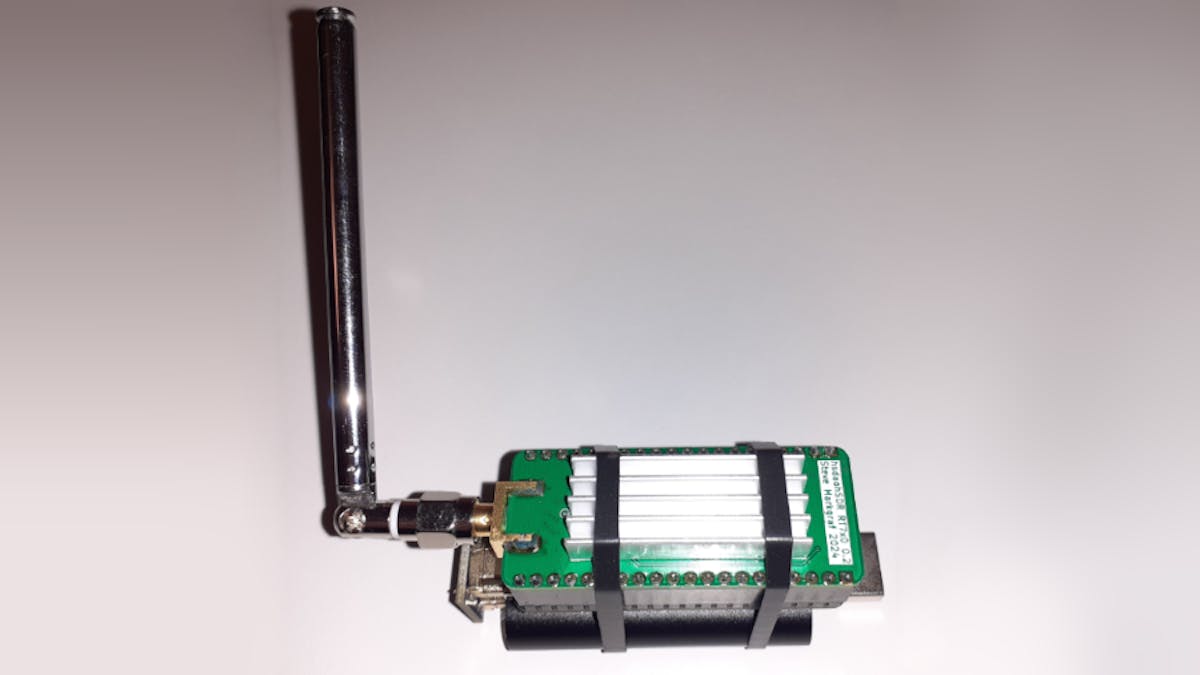

"This project aims to (ab)use cheap USB 3.0 HDMI capture sticks based on the MacroSilicon MS2130 as a general purpose USB interface," Markgraf explans of the "hsdaoh" project. "In combination with small FPGA boards with HDMI interface like the [Sipeed] Tang Nano series, it can be used to capture high speed data streams from an external data source like an ADC [Analog to Digital Converter], do-it-yourself SDR [Software-Defined Radio], or simply build a high speed logic analyzer."

Markgraf's creation aims to work around a gulf in data acquisition performance between easily-implemented USB 2.0, at 480Mb/s, and USB 3.0 at 5Gb/s — "a huge step in hardware complexity," the developer explains of the latter. Rather than implementing USB 3.0 directly on a device, then, hsdaoh takes a different approach: shuffling data as video over HDMI to an HDMI capture dongle that handles the USB 3.0 interface for you.

Compared to off-the-shelf USB 3.0 interfaces, hsdaoh — which can be implemented on an FPGA costing as little as $15, with compatible capture cards based on the Macrosilicon MS2130 or MS2131 chips adding $10 to the bill of materials — is considerably cheaper. It's also easier to implement than rolling your own USB 3.0 interface: just connect the FPGA board to your project and link its HDMI output to the USB dongle and you're done.

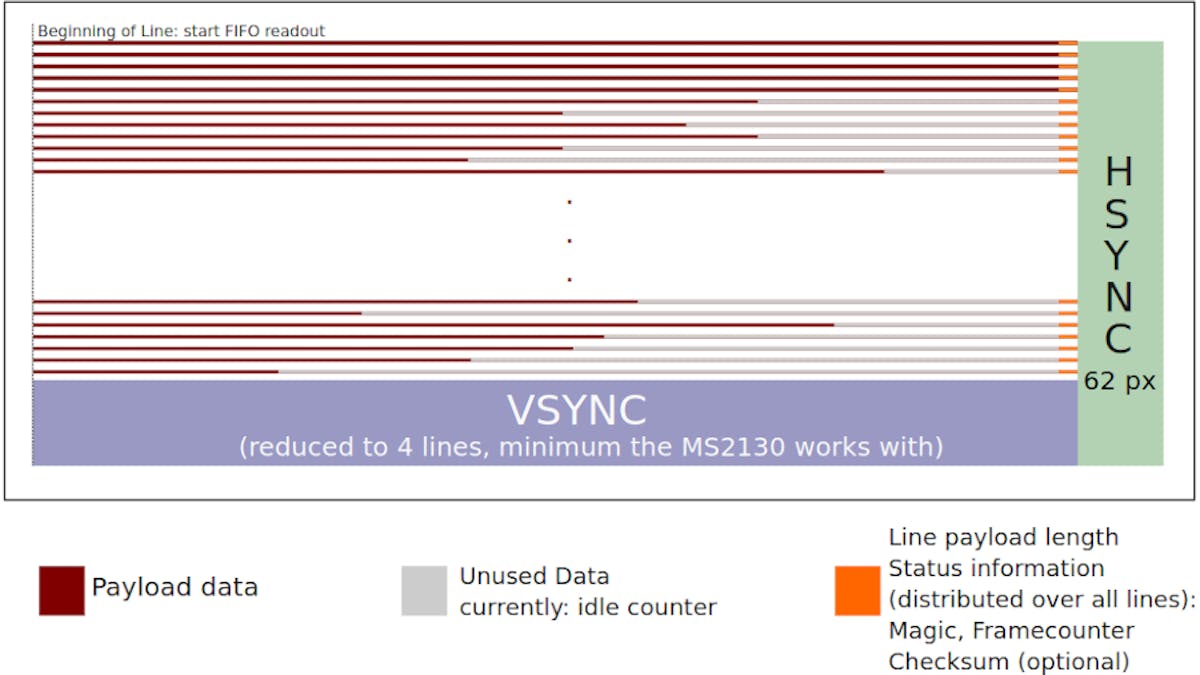

Data captured by the FPGA is encoded as streaming video, made up of horizontal lines that include payload and status data. This is then decoded by a client-side application, either to save as a file or to further stream over a TCP socket to an additional application. Performance varies depending on FPGA — but even the slowest device in the Sipeed Tang Nano family can hit 816Mb/s, nearly double that of USB 2.0, while the fastest reached 1,472Mb/s in Markgraf's testing.

The FPGA source code is available on GitHub under an unspecified license, with a second repository for the client-side application. Markgraf has also designed a software-defined radio (SDR) board based on hsdaoh, available in a separate repository.

Freelance journalist, technical author, hacker, tinkerer, erstwhile sysadmin. For hire: freelance@halfacree.co.uk.