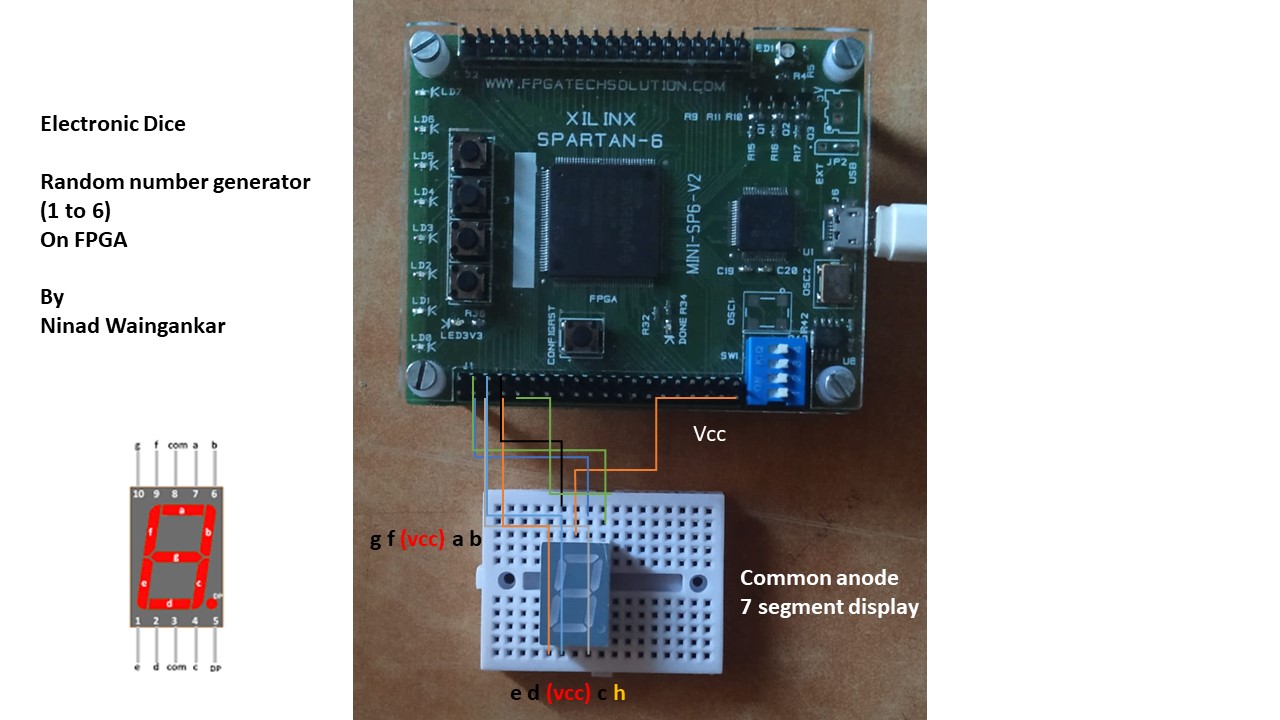

VHDL implementation of random number generator from 1 to 6 (3 bits). The random number is displayed on common anode 7 segment display. Hence it can be used as Electronic dice. Implemented on Xilinx Spartan 6 FPGA..vhd is VHDL file.ucf is user implementation file. assign IO pins on FPGA with pins in the.ucf file. Random number generation is done by continuous XOR operation of bit vector at clock pulses. This project can be used to replace traditional dice used in Ludo game.

Published October 5, 2020

Comments