Oh, the world of digital processing has moved fast this decade! when it comes to high speed digital signal processing, engineers no longer have the simple choice of a digital signal processor. Engineers and hobbyists alike must consider the relatively young and modern SoC (System on Chip). Especially when it comes to very high speed signal processing applications such as RF, the SoC must have an edge over a classical signal processor. Especially the case for the Zynq-7000 SoC which contains a relatively large FPGA (Programmable Logic) and dual (or single according to the chip) core A9 ARM processors (Processing System).

An even more amazing prospective is the combination of such a chip with high speed hardware and interfacing! This would be the Eclypse Z7 board from Digilent, which consists of two Zmod ports which run the high speed open-source SYZYGY standard from Opal Kelly. Together with their Zmod Expansion boards containing a high speed ADC and a DAC (separate boards).

The ProjectSo what we will be doing in this project is to combine the Zynq-7000 chip with the high speed ADC and DAC. Interestingly, this will be done using a hierarchical design which uses both the programmable logic and the processing system of the Zynq-7020. The below figure illustrates the loop of our design.

The input signal will be sampled by the Zmod-ADC which will be run by Digilent's ADC IP. The time domain samples will then be passed to the processing system via an AXI-stream. We will use Digilent's Processing system ADC library to control the ADC parameters and receive the samples in the processing system (PS) part of the SoC. The samples will then be transferred via the processing system to Digilent's DAC library which controls the DAC and will pass the samples to Digilent's DAC IP. The Zmod-DAC will then recreate the samples and output them.

Note:

The Zmod ADC has a high gain input range of +/-1V OR a low gain input range of +/-25V. The Zmod DAC has an output range of ±1.25V (Low Range) OR ±5V (High Range). This means that setting both gains to low, we get a slight shift in voltage at the output, i.e. a greater voltage at the output. This occurs as the voltage ranges of both the Zmods are being mapped to the 14bit total resolution. So there will be a sight change in voltage for the same binary value. Setting the gains differently would present different results! However, if one needs the same voltage at the output, this is possible by scaling the input and output according to the project needs.

ImplementationSo let's get started with the actual implementation. Digilent has kindly provided multiple projects for the DAC and ADC. We will be using Digilent's Zmod Base Library, in particular, the ZMODADC1410 Demo and ZMODDAC1411 Demo (We will be using the bare-metal application for the processing system). if you are using Vivado 2019.1 you can follow their digilent's instructions to successfully open the individual projects in Vivado 2019.1. Since I have migrated to Vivado 2020.1 with the Vivado/Vitis design flow, I will be working on Vivado/Vitis 2020.1. The steps to follow are completely the same!. If you are using Vivado 2020.1, I have migrated the individual ADC and DAC projects for Vivado 2020.1 and the individual ADC and DAC projects for Vitis 2020.1. Also, do not forget to download Digilent's board files for Vivado.

Once you have opened the ADC and DAC demos from Digilent, we can now start to combine the two projects into one.

Combining The DemosThere are multiple ways to combine two Vivado projects, I have chosen to go for creating a new project, importing the block designs from both the ADC and DAC demos. Then copying the IPs and connections from one block design to the other. Finally we have to make some changes such as removing duplicate IPs and connections. The combined demos project in Vivado 2020.1 is linked here.

To combine the two projects create a new project in Vivado, once you arrive at this window, click "Add Files".

The locations of the block designs can be seen by opening the respective project clicking on the block design in the sources window of Vivado and looking at the "Sorce File Properties" Window. The block design files should be named "design_1.bd".

Once the new project has been opened with both block designs imported we can now do the necessary changes. The complete new block design should look something like this:

After the block design has been finished, go to the address editor in Vivado. Right click on one of the IPs and click on "Assign All". In my case below this is not available since all addresses are assigned. These addresses are extremely important in any design since they are the addresses used for inter-IP communication and PS to PL communication via the AXI interface.

When this has been done, go to your block design in the sources window, right click on the block design and click "Create HDL Wrapper".

Now we can finally generate the bitstream by clicking on "Generate Bitstream".

Once Vivado has successfully generated the bitstream, go to file -> Export -> Export Hardware.

Once this window is prompted, click "Fixed" and the click next.

It is important to click "Include Bitstream", then next.

Vivado has now exported the bitstream!!!!

Vitis ProjectWe now have to make a Vitis project where we will design our bare-metal application which will be running on the A9 processor in the Zynq chip. The ADC and DAC project can be downloaded here. The first step is to open a new project in Vitis as follows.

Open Vitis, Define a workspace and click launch.

Once Vitis has opened, go to file and click "import".

Select "Vitis project exported zip file", and click next.

Browse for the zip file with the required project and click next. Here we can see the project files including the hardware specification exported from Vivado. To load the project into the Eclypse, connect the board to your PC.

Now click on the top level project file "ZMOD_DAC_ADC_system" and click the build button.

Finally, right click on the top level project file "ZMOD_DAC_ADC_system", go to run as and click "Launch Hardware".

The project should now be loaded into the Eclypse Z7!!!!!!!!

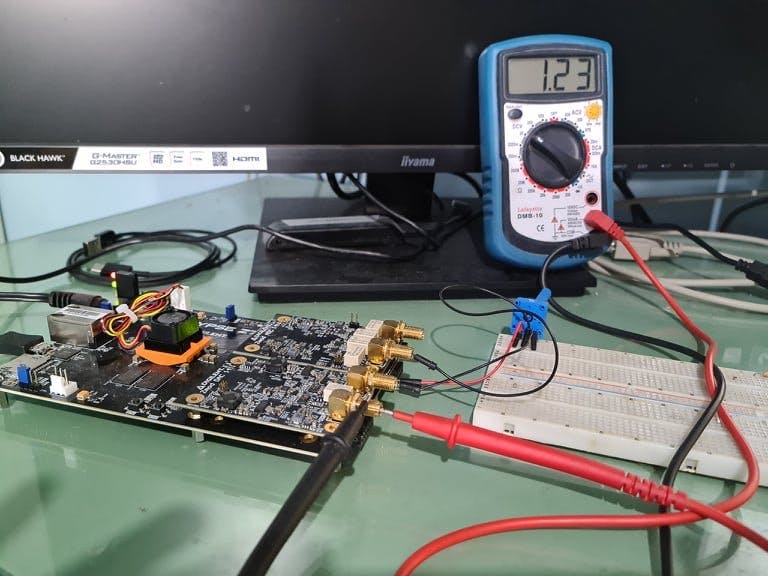

To test the project I suggest using a simple potentiometer (you can use the 3.3V supply from the Pmod connector on the bottom of the board) for the ADC input. And reading from the DAC via a multimeter.

Turning the potentiometer should result in a different voltage on the output of the Zmod DAC!

ConclusionI hope you have found this tutorial and it's attachments helpful, this project could be used to implement any king of signal processing technique in the processing system of the Zynq chip, which is incorporated with two Zmod high speed ADC/DAC on the wonderful Eclypse Z7.

Comments

Please log in or sign up to comment.