Hardware components | ||||||

|

| × | 1 | |||

|

| × | 1 | |||

|

| × | 1 | |||

|

| × | 1 | |||

Software apps and online services | ||||||

|

| |||||

|

| |||||

|

| |||||

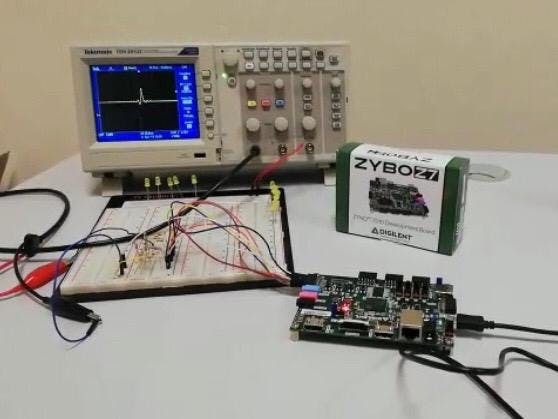

This project aims to create transmission line between two links using FPGA cards and solve the synchronization problems with ADPLL. Analog communication and synchronization systems are always been popular but not quite effective for any communication system. This project uses digital data bits to send any messages through any communication link with minimum phase errors.

In this project, QAM communication technique is used. Since in QAM there are two coefficients, in every 2 bits data is ready to send. In the end of the video below transmitter part of the each case of signals can be observed in order [00 01 10 11].

.

clc;clear all;

Tc=1/25.5;

a=0.22;

% t=-12.7*1.5:0.15:12.8*1.5;

t=-38.22*Tc:2.56*4*Tc:38.22*Tc;

p=zeros(1,length(t));

for i=1:1:length(t)

if t(i)==0

p(i)= (1-a)+4*a/pi;

else if t(i)==1/(4*a) || t(i)==-1/(4*a)

p(i)=a/sqrt(2)*((1+2/pi)*sin(pi/(4*a))+(1-2/pi)*cos(pi/(4*a)));

else

p(i) = (sin(pi*t(i)*(1-a))+4*a*t(i).*cos(pi*t(i)*(1+a)))./(pi*t(i).*(1-(4*a*t(i)).^2));

end

end

end

%carriers1

c1=(cos(2*pi*t/Tc));

c2=(sin(2*pi*(t)/Tc));

% carriers2

cr1=(cos(2*pi*t/Tc));

cr2=(sin(2*pi*(t)/Tc));

a=1;b=1;

y1=(a*p.*c1+b*p.*c2);

y2=(-a*p.*c1-b*p.*c2);

y3=(a*p.*c1-b*p.*c2);

y4=(-a*p.*c1+b*p.*c2);

% figure(1)

% plot(t,y1)

yr11=(cr1.*y1);

yr12=(cr2.*y1);

yr21=(cr1.*y2);

yr22=(cr2.*y2);

yr31=(cr1.*y3);

yr32=(cr2.*y3);

yr41=(cr1.*y4);

yr42=(cr2.*y4);

k11=yr11.*p;

k12=yr12.*p;

k21=yr21.*p;

k22=yr22.*p;

k31=yr31.*p;

k32=yr32.*p;

k41=yr41.*p;

k42=yr42.*p;

z=0;

y=0;

f=0;

s=0;

u=0;

l=0;

q=0;

x=0;

for w=1:1:length(t)

z=k11(w)+z;

y=k12(w)+y;

f=k21(w)+f;

s=k22(w)+s;

u=k31(w)+u;

l=k32(w)+l;

q=k41(w)+q;

x=k42(w)+x;

end

vecd=[z y f s u l q x] ;

rec=zeros(1,length(vecd));

% % % stem(vecd)

% % % axis([-5 15 20 -20])

for que=1:1:length(vecd)

if vecd(que)>=0

rec(que)=1;

elseif vecd(que)<=0

rec(que)=0;

end

end

subplot(2,1,1)

stem(vecd)

axis([-1 9 -2 2])

title('QAM Coefficients That Received')

ylabel('QAM Coefficients')

xlabel('Data Vectors Order')

subplot(2,1,2)

stem(rec)

ylabel('Data Has Been Sent')

xlabel('Sended Bit Vector')

axis([-1 9 -2 2])

title('Initial Data Vectors That Detected')

% figure(8)

% plot(t,p.*c2)

clc;clear all;

Tc=5;

a=0.02;

t=-12.7*1.5:0.15:12.8*1.5;

% t=-38.22*Tc:2.56*4*Tc:38.22*Tc;

c1=cos(2*pi*t/Tc);

c2=sin(2*pi*(t)/Tc);

p=zeros(1,length(t));

for i=1:1:length(t)

if t(i)==0

p(i)= (1-a)+4*a/pi;

else if t(i)==1/(4*a) || t(i)==-1/(4*a)

p(i)=a/sqrt(2)*((1+2/pi)*sin(pi/(4*a))+(1-2/pi)*cos(pi/(4*a)));

else

p(i) = (sin(pi*t(i)*(1-a))+4*a*t(i).*cos(pi*t(i)*(1+a)))./(pi*t(i).*(1-(4*a*t(i)).^2));

end

end

end

figure(1)

plot(t,p)

hold on

plot(t,p.*c1)

title('Square-Root Raised Cosine Filter Filling with Cosine Signal')

ylabel('Amplitude')

xlabel('Time')

grid on

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity bitirme_2 is

port( clk_in: in std_logic;

X:in std_logic_vector(1 downto 0);

output:out std_logic_vector(7 downto 0) );

end entity;

architecture logic_flow of bitirme_2 is

type matrix is array(0 to 255) of integer range 0 to 255;

signal y: matrix;

signal count: natural range 1 to 50000;

signal count2: natural range 0 to 255;

signal temp_clk_out: std_logic:='0';

signal temp_clk_out_in: std_logic:='0';

signal i:integer:=0;

signal q:integer;

signal z:std_logic_vector(7 downto 0);

signal CON:std_logic_vector(1 downto 0);

signal count3:natural range 1 to 256;

signal clk_out_divided: std_logic;

signal clk_256: std_logic;

signal clk_out_original : std_logic;

begin

z<="10000111";

process(z,clk_256)

variable c : integer range 0 to 8 :=0;

begin

--i<=0;

if(rising_edge(clk_256))then

if (c < 7) then

CON<=(z(c)&z(c+1));

c := c+2;

else

c:=0;

end if;

if(X="00")then

--y1

y<=(127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,126,126,126,127,127,128,128,128,127,127,127,126,126,126,127,127,127,127,127,127,127,127,127,127,127,127,126,126,125,125,126,128,129,131,131,130,128,124,121,119,119,121,126,130,135,137,136,133,129,125,122,122,125,128,129,125,115,97,73,46,23,6,0,8,28,57,89,119,143,157,160,155,145,133,122,116,114,114,120,124,128,130,130,129,128,127,127, 127,128,128,128,127,126,126,125,126,126,127,128,128,128,128,127,126,126,126,126,127,127,128,128,128,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,126,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127);--y1

--y2

elsif(X="01")then

y<=(126,126,127,127,126,126,126,126,126,126,127,127,127,127,127,127,126,126,126,126,126,127,127,127,127,127,126,126,126,126,126,126,127,127,127,127,126,127,127,127,127,127,127,126,126,126,126,126,127,127,127,127,127,127,126,126,126,126,126,127,127,127,127,127,126,126,126,126,126,127,126,126,126,126,126,126,127,127,127,127,127,126,126,125,125,126,126,127,128,128,128,127,126,125,125,125,126,127,127,128,127,127,127,127,128,129,130,129,127,124,119,115,113,115,122,133,145,155,160,156,143,119,89,56,28,8,0,6,22,46,72,96,114,125,129,127,124,122,122,124,129,133,136,137,134,130,125,121,119,119,121,124,127,130,131,130,129,127,126,125,125,125,126,127,127,127,127,127,126,127,127,127,127,127,126,126,126,126,126,127,127,127,127,127,127,126,126,126,126,126,126,127,127,127,127,127,126,126,126,126,126,127,127,126,126,126,126,127,127,127,127,127,126,126,126,126,126,126,127,127,127,127,127,126,126,126,126,126,126,127,127,127,127,127,126,126,127,127,127,126,126,126,126,126,126,127,127,127,127,127,127,126,126,126,126,126);--y2

--y3

elsif(X="10")then

y<=(127,127,127,126,127,127,127,127,127,127,126,126,126,126,126,126,127,127,127,127,127,126,126,126,126,126,127,127,127,127,127,127,126,126,126,126,127,126,126,126,126,126,126,127,127,127,127,127,126,126,126,126,126,126,127,127,127,127,127,126,126,126,126,126,127,127,127,127,127,126,127,127,127,127,127,127,126,126,126,126,126,127,127,128,128,127,127,126,125,125,125,126,127,128,128,128,127,126,126,125,126,126,127,126,125,124,123,124,126,129,134,138,140,138,131,120,108,98,93,97,110,134,164,197,225,245,253,247,231,207,181,157,139,128,124,126,129,131,131,129,124,120,117,116,119,123,128,132,134,134,132,129,126,123,122,123,124,126,127,128,128,128,127,126,126,126,126,126,127,126,126,126,126,126,127,127,127,127,127,126,126,126,126,126,126,127,127,127,127,127,127,126,126,126,126,126,127,127,127,127,127,126,127,127,127,127,127,126,126,126,126,126,127,127,127,127,127,127,126,126,126,126,126,127,127,127,127,127,127,126,126,126,126,126,127,127,126,126,126,127,127,127,127,127,127,126,126,126,126,126,126,127,127,127,127,127);

--y4=

else

y<=(127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,126,126,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,127,126,127,127,127,128,128,128,127,127,126,126,126,126,127,127,128,128,128,127,127,127,127,127,127,127,127,126,126,126,127,127,128,129,129,128,126,124,123,123,124,126,130,133,135,135,132,128,123,119,116,117,120,124,129,131,131,129,126,124,128,139,157,181,207,231,247,253,245,225,197,165,134,110,97,93,98,108,120,131,138,140,138,134,130,126,124,123,124,125,126,127,126,126,125,126,126,127,128,128,128,127,126,125,125,125,126,127,127,128,128,127,127,126,126,126,126,126,127,127,127,127,127,127,126,127,127,127,127,127,126,126,126,126,126,127,127,127,127,127,126,126,126,126,126,126,127,127,127,127,127,126,126,126,126,126,126,127,126,126,126,126,127,127,127,127,127,127,126,126,126,126,126,127,127,127,127,127,126,126,126,126,126,126,127,127,127,127,127,127,126,127,127,127,127);

end if;

i<=i+2;

end if;

end Process;

clk_out_original <= clk_in;

process(clk_in)

begin

if (rising_edge(clk_in)) then

count <= count + 1;

if(count=50000) then

temp_clk_out<=not temp_clk_out;

count<=1;

end if;

end if;

end process;

clk_out_divided <= temp_clk_out;

process(clk_out_divided)

begin

if (rising_edge(clk_out_divided)) then

count3 <= count3 + 1;

if(count3=256) then

temp_clk_out_in<=not temp_clk_out_in;

count3<=1;

end if;

end if;

end process;

clk_256<=temp_clk_out_in;

process(clk_out_divided)

begin

if (rising_edge(clk_out_divided)) then

output<= conv_std_logic_vector( y(count2),8 );

if(count2=255) then

count2<=0;

end if;

count2 <= count2 + 1;

end if;

end process;

end architecture;

# ADPLL-Design-for-Transciever-System

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Design Name:

-- Module Name: PLL_CO_BO - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_misc.all;

use IEEE.std_logic_unsigned.all;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity PLL_CO_BO is

port (

clk: in STD_LOGIC; -- clock for k and id counter

f_in: in STD_LOGIC; -- input signal

dn_up:in STD_LOGIC;

f_out: inout STD_LOGIC; -- output signal

k_up_out:out STD_LOGIC_VECTOR(3 downto 0);

Bo_out:out STD_LOGIC;

Ca_out:out STD_LOGIC;

ID_out_out:out STD_LOGIC;

tog_FF_out:out STD_LOGIC;

k_dn_out:out STD_LOGIC_VECTOR(3 downto 0)

);

end PLL_CO_BO;

architecture Behavioral of PLL_CO_BO is

constant Kbit: integer:=4;

constant counter: natural range 1 to 2:=1;

signal Ca: std_logic:='0'; -- carry out of k_counter

signal Bo: std_logic:='0'; -- borrow out of k_counter

signal k_up: std_logic_vector (Kbit-1 downto 0):="0000"; -- up counter in k_counter

signal k_dn: std_logic_vector (Kbit-1 downto 0):="0000"; -- down counter in k_counter

signal k_half: std_logic_vector (Kbit-1 downto 0):="0100"; -- up counter in k_counter

signal tog_FF: std_logic:='0';

signal ID_Out:std_logic:='0';

signal temp_clk_out: std_logic :='0';

signal k_up_before: std_logic_vector (Kbit-1 downto 0):="0000"; -- up counter in k_counter before

signal k_dn_before: std_logic_vector (Kbit-1 downto 0):="0000"; -- down counter in k_counter before

begin

k_cnt: process (clk)

begin

if clk='0' and clk'event then

if dn_up='1' then

k_up <= k_up;

k_dn<=k_dn+1;

else

k_dn <= k_dn;

k_up<=k_up+1;

end if;

if k_dn = Kbit+Kbit then

k_dn <= (others=>'0');

end if;

if k_up = Kbit+Kbit then

k_up<= (others=>'0');

end if;

--carry barrow belirleme

if k_up >= k_half then

Ca<='1';

else

Ca<='0';

end if;

if k_dn >= k_half then

Bo<='1';

else

Bo<='0';

end if;

end if;

end process;

k_up_out<=k_up;

k_dn_out<=k_dn;

Ca_out<=Ca;

Bo_out<=Bo;

ID_Count: process (clk)

begin

if clk='0' and clk'event then

if ((k_up=k_half or k_up=k_half+1) and (k_up_before /= k_up)) then

tog_FF<='0';

end if;

end if;

if clk='1' and clk'event then

if ((k_dn=k_half or k_dn=k_half+1) and (k_dn_before /= k_dn)) then

tog_FF<= '1';

else

if ((k_up=k_half or k_up=k_half+1) and (k_up_before/=k_up)) then

tog_FF<=tog_FF;

else

tog_FF<=not tog_ff;

end if;

end if;

ID_Out<=not(clk or tog_FF);

k_up_before<=k_up;

k_dn_before<=k_dn;

end if;

end process;

ID_out_out<=ID_Out;

tog_FF_out<=tog_FF;

end Behavioral;

--------------------------------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY TBCABO_8 IS

END TBCABO_8;

ARCHITECTURE behavior OF TBCABO_8 IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT PLL_CO_BO

PORT(

clk : IN std_logic;

f_in : IN std_logic;

dn_up : IN std_logic;

f_out : INOUT std_logic;

k_up_out : OUT std_logic_vector(3 downto 0);

Bo_out : OUT std_logic;

Ca_out : OUT std_logic;

ID_out_out : OUT std_logic;

tog_FF_out : OUT std_logic;

k_dn_out : OUT std_logic_vector(3 downto 0)

);

END COMPONENT;

--Inputs

signal clk : std_logic := '0';

signal f_in : std_logic := '0';

signal dn_up : std_logic := '0';

--BiDirs

signal f_out : std_logic;

--Outputs

signal k_up_out : std_logic_vector(3 downto 0);

signal Bo_out : std_logic;

signal Ca_out : std_logic;

signal ID_out_out : std_logic;

signal tog_FF_out : std_logic;

signal k_dn_out : std_logic_vector(3 downto 0);

signal k_up_before: std_logic_vector (3 downto 0);

signal k_dn_before: std_logic_vector (3 downto 0);

-- Clock period definitions

constant clk_period : time :=50 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: PLL_CO_BO PORT MAP (

clk => clk,

f_in => f_in,

dn_up => dn_up,

f_out => f_out,

k_up_out => k_up_out,

Bo_out => Bo_out,

Ca_out => Ca_out,

ID_out_out => ID_out_out,

tog_FF_out => tog_FF_out,

k_dn_out => k_dn_out

);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

-- hold reset state for 100 ns.

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='0';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

dn_up<='1';

wait for 100 ns;

--wait for clk_period*10;

-- insert stimulus here

wait;

end process;

END;

3 projects • 3 followers

This team was created by Hasan Toskar & Seda Esen & Berkay Ergün

0 projects • 1 follower

Connection mail ergnberkay@gmail.com or vhdlcankaya@gmail.com

Thanks to Orhan Gazi.

Comments

Please log in or sign up to comment.