As we already developed the "DPU TRD with ZCU104" with DPU version 2.0 earlier in May 2019. This time we have developed the DPU TRD for ZCU104 with DPU IP version 3.0 [though DPU IP version 3.1 was just released two days back, dec 2, 2019].We are testing the resnet50 as the default design of TRD on this test to.

The main design flow covers same as the previos DPU TRD which we publish here at Hackster and Logictronix.com. We have updated the Tcl script from the old DPU TRD, created the project on the base of DPU (3.0) TRD for ZCU102 added "Softmax function" and few other features on the VIVADO design.

On the petalinux build we have used the BSP of ZCU102 provided at the DPU TRD v3.0 for ZCU102, we changed the board setting from the DTG settings, and we updated the device tree for our updated interrupt and softmax. Then we created the BOOT.BIN.

Unfortunately, the DPU 3.0 provided at DPU TRD v3.0 for ZCU102 has timelimt of 8 hours, this time limit start from the time when you synthesized the project[PG338 v3.0 says: "the DPU records the time that the DPU project was synthesized"]. So we have developed the ZCU104 TRD with single DPU core and other feature enabled so that we could develop [create BOOT.BIN] the design on our normal Ubuntu Host Machine and test it on ZCU104 FPGA.

And our test got success on the few attempts [due to our resource optimization plan and time limit].

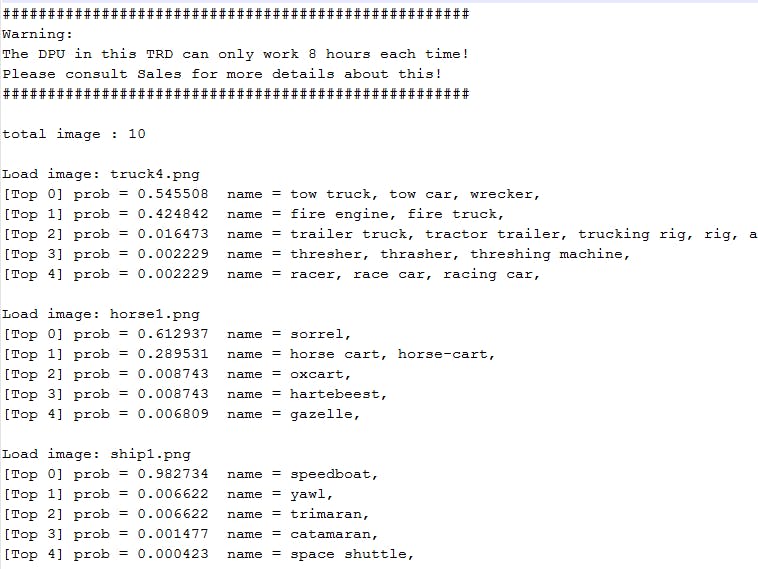

And here is the test result:

If you are interested to test the BOOT.BIN and explore on it then please write us at: info@logictronix.com. We can send the BOOT.BIN as the email request.

![LogicTronix [FPGA Design + Machine Learning Company]](https://hackster.imgix.net/uploads/attachments/1123066/_SyVIfEqFUU.blob?auto=compress%2Cformat&w=40&h=40&fit=min&dpr=2)

![LogicTronix [FPGA Design + Machine Learning Company]](https://hackster.imgix.net/uploads/attachments/1123066/_SyVIfEqFUU.blob?auto=compress%2Cformat&w=60&h=60&fit=min&dpr=2)

Comments

Please log in or sign up to comment.