At the start of any image processing development, one of the first things we want to do is to verify the hardware configuration. At a simple level this is demonstrating if our chosen development board can interface with the selected cameras while achieving the desired performance.

Such an approach enables the technology readiness level of the solution to be incrementally increased.

In this first project we are going to create a bare metal application which will enable us to demonstrate

- Vivado configuration necessary for communicating with the PCam5C imager

- Software settings to configure the camera for 720P output

- Display Port Settings for the output video.

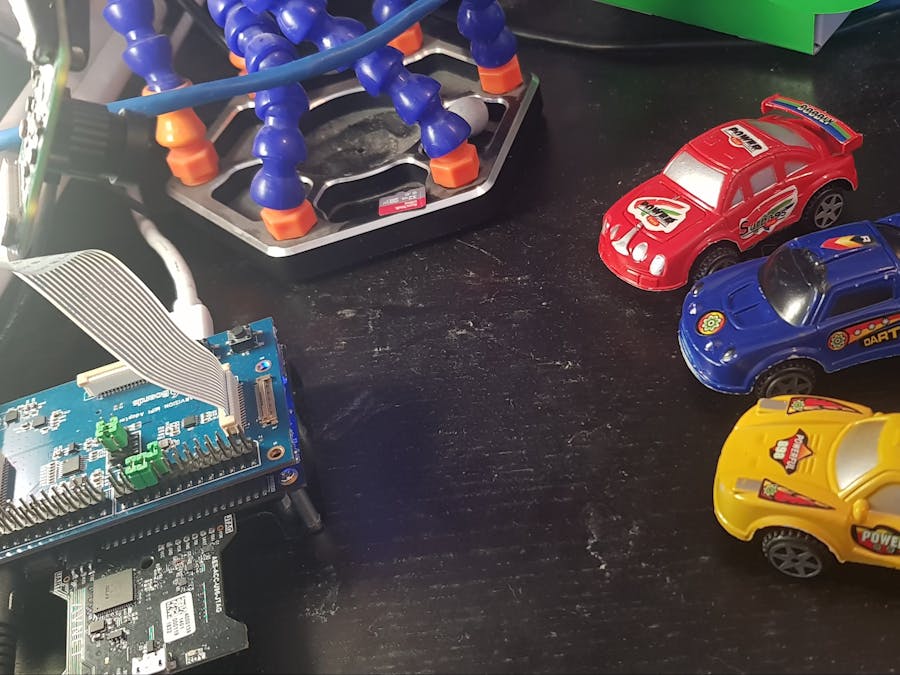

The hardware needed for this session and all the sessions is shown below. A Ultra96V2, MIPI Interface board, PCAM 5C camera and JTAG/UART Pod.

This project has been created using Vivado 2019.2 and uses only existing Xilinx IP cores, there is no requirement to generate any custom RTL or HLS modules.

While the MIPI IP cores require a license as part of the 2019.2 tool chain, from 2020.1 the MIPI cores are included within the tool without separate license.

To create the design we need the following IP blocks

- MIPI CSI2 RX SubSystem

- Demosaic

- Gamma LUT

- Video Direct Memory Access

- Clock Wizard

- Video Timing Controller

- AXI Stream to Video Out

- Zynq MPSoC Processing Core

Along with these blocks AXI Smart Connects and AXI Interconnects are used to connect the AXI networks used for configuration of the IP cores and the transfer of images to and from the PS DDR Memory.

The project also uses AXI Subset converters to reduce the number of pixels per bit from the 10 bit per pixel output by the MIPI block to 8 bit per pixel for downstream processing. AXI Subset converters are used to rearrange the RBG pixel format to a RGB format.

The settings for the IP Blocks are

To save on the implementation resources the number of columns and rows were reduced

The same approach is taken with the Gamma LUT

The VDMA transfers data to and from the Processor DDR system

The Video Timing Controller is used to generate the timing for the output video

The final element in the processing pipeline is the AXI Stream to Video Out

The clocking infrastructure is the following, the 200 MHz cock is provided to the MIPI DPHY reference, while the 150 MHz provides the clocking for the AXI Stream and hence the processing chain.

A second clock wizard is used to generate the output pixel clock timing.

The clocking network is as below, all clock wizards were generated from a 100 MHz PL Clock

The completed Vivado Design looks as below in the diagram

Once the design is built we can export the XSA to Vitis to create the software application.

VITIS Application DevelopmentThe VITIS software is required to configure the camera, image processing pipeline and the display port output.

Of course, the first thing we need to do is create the platform for the development, this will create us the boot files and the board support package and associated software API's necessary to support our development.

Using the API's provided by Xilinx the development of the application is quite simple.

The software application therefore performs the following steps

- Initialize the GPIO and enable the camera using the GPIO signal

- Initialize the I2C, VTC, VDMA, Demosaic and GAMMA LUT

- Configure the camera over the I2C link for 720P performance

- Configure the VTC for 1280 by 720 P performance

- Configure the VDMA and its frame buffers in the PS DDR

- Enable the Demosaic

- Calculate the GAMMA LUT values

- Start the image processing

The application software developed can be seen below

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"

#include "xvtc.h"

#include "vga_modes.h"

#include "xvidc.h"

#include "xavbuf.h"

#include "xavbuf_clk.h"

#include "xvidc.h"

#include "xdpdma_video_example.h"

#include "xaxivdma.h"

#include "xaxivdma_i.h"

#include "i2c.h"

#include "xgpiops.h"

#include "xiicps.h"

#include "xv_demosaic.h"

#include "xv_gamma_lut.h"

#include "math.h"

XIicPs iic_cam;

XGpioPs gp_cam;

XAxiVdma vdma;

XAxiVdma_DmaSetup vdmaDMA;

XAxiVdma_Config *vdmaConfig;

XVtc VtcInst;

XVtc_Config *vtc_config ;

VideoMode video;

XV_demosaic cfa;

XV_gamma_lut gamma_inst;

#define DEMO_MAX_FRAME (720*1280)

#define DEMO_STRIDE (1280*3)

#define DISPLAY_NUM_FRAMES 1

#define cam_gpio XPAR_XGPIOPS_0_DEVICE_ID

#define IIC_cam XPAR_XIICPS_0_DEVICE_ID

#define CAM_ID 0x78

#define IIC_CAM_ADDR 0x3c

#define IIC_SCLK_RATE 100000

#define SW_IIC_ADDR 0x75

void detect_camera();

int Initial_setting_1 ( u32 *cfg_init , int cfg_init_QTY );

void gamma_calc(float gamma_val);

u8 SendBuffer [10];

u8 RecvBuffer [10];

u16 gamma_reg[1024];

u32 frameBuf[DISPLAY_NUM_FRAMES][DEMO_MAX_FRAME];

u32 *pFrames[DISPLAY_NUM_FRAMES];

int main()

{

XVtc_Timing vtcTiming;

XVtc_SourceSelect SourceSelect;

VideoMode video;

XGpioPs_Config *GPIO_Config;

XIicPs_Config *iic_conf;

int Status;

init_platform();

print("Hello World\n\r");

GPIO_Config = XGpioPs_LookupConfig(cam_gpio);

Status= XGpioPs_CfgInitialize(&gp_cam,GPIO_Config,GPIO_Config->BaseAddr);

XGpioPs_SetOutputEnablePin(&gp_cam,37,1);

XGpioPs_SetDirectionPin(&gp_cam,37,1);

XGpioPs_WritePin(&gp_cam,37,0x0);

usleep(1000000);

XGpioPs_WritePin(&gp_cam,37,0x1);

iic_conf = XIicPs_LookupConfig(IIC_cam);

XIicPs_CfgInitialize(&iic_cam,iic_conf,iic_conf->BaseAddress);

XIicPs_SetSClk(&iic_cam, IIC_SCLK_RATE);

vtc_config = XVtc_LookupConfig(XPAR_VTC_0_DEVICE_ID);

XVtc_CfgInitialize(&VtcInst, vtc_config, vtc_config->BaseAddress);

//run_dppsu();

///set the I2C Switch

SendBuffer[0]= 0x04;

Status = XIicPs_MasterSendPolled(&iic_cam, SendBuffer, 1, SW_IIC_ADDR);

if (Status != XST_SUCCESS) {

//print("I2C write error\n\r");

return XST_FAILURE;

}

//detect camera

detect_camera();

//configure camera

SendBuffer[0]= 0x31;

SendBuffer[1]= 0x03;

SendBuffer[2]= 0x11;

Status = XIicPs_MasterSendPolled(&iic_cam, SendBuffer, 3, IIC_CAM_ADDR);

SendBuffer[0]= 0x30;

SendBuffer[1]= 0x08;

SendBuffer[2]= 0x82;

Status = XIicPs_MasterSendPolled(&iic_cam, SendBuffer, 3, IIC_CAM_ADDR);

usleep(1000000);

Initial_setting_1 ( cfg_init , 63 );

Initial_setting_1 ( cfg_720p_60fps , 38 );

xil_printf("Configuration Complete\n\r");

//set up the video timing controller

video = VMODE_1280x720;

vtcTiming.HActiveVideo = video.width; /**< Horizontal Active Video Size */

vtcTiming.HFrontPorch = video.hps - video.width; /**< Horizontal Front Porch Size */

vtcTiming.HSyncWidth = video.hpe - video.hps; /**< Horizontal Sync Width */

vtcTiming.HBackPorch = video.hmax - video.hpe + 1; /**< Horizontal Back Porch Size */

vtcTiming.HSyncPolarity = video.hpol; /**< Horizontal Sync Polarity */

vtcTiming.VActiveVideo = video.height; /**< Vertical Active Video Size */

vtcTiming.V0FrontPorch = video.vps - video.height; /**< Vertical Front Porch Size */

vtcTiming.V0SyncWidth = video.vpe - video.vps; /**< Vertical Sync Width */

vtcTiming.V0BackPorch = video.vmax - video.vpe + 1;; /**< Horizontal Back Porch Size */

vtcTiming.V1FrontPorch = video.vps - video.height; /**< Vertical Front Porch Size */

vtcTiming.V1SyncWidth = video.vpe - video.vps; /**< Vertical Sync Width */

vtcTiming.V1BackPorch = video.vmax - video.vpe + 1;; /**< Horizontal Back Porch Size */

vtcTiming.VSyncPolarity = video.vpol; /**< Vertical Sync Polarity */

vtcTiming.Interlaced = 0;

memset((void *)&SourceSelect, 0, sizeof(SourceSelect));

SourceSelect.VBlankPolSrc = 1;

SourceSelect.VSyncPolSrc = 1;

SourceSelect.HBlankPolSrc = 1;

SourceSelect.HSyncPolSrc = 1;

SourceSelect.ActiveVideoPolSrc = 1;

SourceSelect.ActiveChromaPolSrc= 1;

SourceSelect.VChromaSrc = 1;

SourceSelect.VActiveSrc = 1;

SourceSelect.VBackPorchSrc = 1;

SourceSelect.VSyncSrc = 1;

SourceSelect.VFrontPorchSrc = 1;

SourceSelect.VTotalSrc = 1;

SourceSelect.HActiveSrc = 1;

SourceSelect.HBackPorchSrc = 1;

SourceSelect.HSyncSrc = 1;

SourceSelect.HFrontPorchSrc = 1;

SourceSelect.HTotalSrc = 1;

XVtc_RegUpdateEnable(&VtcInst);

XVtc_SetGeneratorTiming(&VtcInst, &vtcTiming);

XVtc_SetSource(&VtcInst, &SourceSelect);

XVtc_EnableGenerator(&VtcInst);

XVtc_Enable(&VtcInst);

for (int i = 0; i < 1; i++)

{

pFrames[i] = frameBuf[i];

}

vdmaConfig = XAxiVdma_LookupConfig(XPAR_AXIVDMA_0_DEVICE_ID);

XAxiVdma_CfgInitialize(&vdma, vdmaConfig, vdmaConfig->BaseAddress);

//video = VMODE_1280x720;

vdmaDMA.FrameDelay = 0;

vdmaDMA.EnableCircularBuf = 1;

vdmaDMA.EnableSync = 0;

vdmaDMA.PointNum = 0;

vdmaDMA.EnableFrameCounter = 0;

vdmaDMA.VertSizeInput = video.height;

vdmaDMA.HoriSizeInput = (video.width)*3;

vdmaDMA.FixedFrameStoreAddr = 0;

vdmaDMA.FrameStoreStartAddr[0] = (u32) pFrames[0];

vdmaDMA.Stride = (video.width)*3;

XAxiVdma_DmaConfig(&vdma, XAXIVDMA_WRITE, &(vdmaDMA));

Status = XAxiVdma_DmaSetBufferAddr(&vdma, XAXIVDMA_WRITE,vdmaDMA.FrameStoreStartAddr);

XAxiVdma_DmaConfig(&vdma, XAXIVDMA_READ, &(vdmaDMA));

XAxiVdma_DmaSetBufferAddr(&vdma, XAXIVDMA_READ,vdmaDMA.FrameStoreStartAddr);

xil_printf("frame addr %x\n\r",vdmaDMA.FrameStoreStartAddr[0]);

XV_demosaic_Initialize(&cfa, XPAR_V_DEMOSAIC_0_DEVICE_ID);

XV_demosaic_Set_HwReg_width(&cfa, video.width);

XV_demosaic_Set_HwReg_height(&cfa, video.height);

XV_demosaic_Set_HwReg_bayer_phase(&cfa, 0x03);

XV_demosaic_EnableAutoRestart(&cfa);

XV_demosaic_Start(&cfa);

gamma_calc(1.2);

XV_gamma_lut_Initialize(&gamma_inst, XPAR_V_GAMMA_LUT_0_DEVICE_ID);

XV_gamma_lut_Set_HwReg_width(&gamma_inst, video.width);

XV_gamma_lut_Set_HwReg_height(&gamma_inst, video.height);

XV_gamma_lut_Set_HwReg_video_format(&gamma_inst, 0x00);

XV_gamma_lut_Write_HwReg_gamma_lut_0_Bytes(&gamma_inst, 0,(int *) gamma_reg, 512);

XV_gamma_lut_Write_HwReg_gamma_lut_1_Bytes(&gamma_inst, 0,(int *) gamma_reg, 512);

XV_gamma_lut_Write_HwReg_gamma_lut_2_Bytes(&gamma_inst, 0,(int *) gamma_reg, 512);

XV_gamma_lut_Start(&gamma_inst);

XV_gamma_lut_EnableAutoRestart(&gamma_inst);

detect_camera();

SendBuffer[0]= 0x31;

SendBuffer[1]= 0x03;

SendBuffer[2]= 0x11;

Status = XIicPs_MasterSendPolled(&iic_cam, SendBuffer, 3, IIC_CAM_ADDR);

//writeReg(0x3103, 0x11);

//[7]=1 Software reset; [6]=0 Software power down; Default=0x02

SendBuffer[0]= 0x30;

SendBuffer[1]= 0x08;

SendBuffer[2]= 0x82;

Status = XIicPs_MasterSendPolled(&iic_cam, SendBuffer, 3, IIC_CAM_ADDR);

//writeReg(0x3008, 0x82);

usleep(1000000);

Initial_setting_1 ( cfg_init , 63 );

Initial_setting_1 ( cfg_simple_awb, 19 );

Initial_setting_1 ( cfg_720p_60fps , 38 );

xil_printf("Configuration Complete\n\r");

Status = XAxiVdma_DmaStart(&vdma, XAXIVDMA_WRITE);

Status = XAxiVdma_StartParking(&vdma, 0, XAXIVDMA_WRITE);

XAxiVdma_DmaStart(&vdma, XAXIVDMA_READ);

XAxiVdma_StartParking(&vdma, 0, XAXIVDMA_READ);

run_dppsu();

while(1){

}

cleanup_platform();

return 0;

}

void detect_camera()

{

u32 Status;

SendBuffer[0]= 0x31;

SendBuffer[1]= 0x00;

Status = XIicPs_MasterSendPolled(&iic_cam, SendBuffer, 2, IIC_CAM_ADDR);

if (Status != XST_SUCCESS) {

print("I2C write error\n\r");

return XST_FAILURE;

}

Status = XIicPs_MasterRecvPolled(&iic_cam, RecvBuffer,1, IIC_CAM_ADDR);

if (Status != XST_SUCCESS) {

print("I2C read error\n\r");

return XST_FAILURE;

}

if(RecvBuffer[0] != CAM_ID ){

print("Camera not detected\n\r");

}

else{

print("Camera detected \n\r");

}

}

int Initial_setting_1 ( u32 *cfg_init , int cfg_init_QTY )

{

s32 Status , byte_count;

int i ;

u8 SendBuffer[10];

for(i=0;i<(cfg_init_QTY*2);i+=2){

SendBuffer[1]= *(cfg_init + i);

SendBuffer[0]= (*(cfg_init + i))>>8;

SendBuffer[2]= *(cfg_init + i + 1);

Status = XIicPs_MasterSendPolled(&iic_cam, SendBuffer, 3, IIC_CAM_ADDR);

if (Status != XST_SUCCESS) {

print("I2C read error\n\r");

return XST_FAILURE;

}

usleep(1000);

}

return XST_SUCCESS;

}

void gamma_calc(float gamma_val)

{

int i;

for(i = 0; i<256; i++){

gamma_reg[i] = (pow((i / 256.0), (1/gamma_val)) * 256.0);

}

}The configuration data for the I2C file can be seen below

static u32 cfg_init [][2] =

{

//[7]=0 Software reset; [6]=1 Software power down; Default=0x02

{0x3008, 0x42},

//[1]=1 System input clock from PLL; Default read = 0x11

{0x3103, 0x03},

//[3:0]=0000 MD2P,MD2N,MCP,MCN input; Default=0x00

{0x3017, 0x00},

//[7:2]=000000 MD1P,MD1N, D3:0 input; Default=0x00

{0x3018, 0x00},

//[6:4]=001 PLL charge pump, [3:0]=1000 MIPI 8-bit mode

{0x3034, 0x18},

//PLL1 configuration

//[7:4]=0001 System clock divider /1, [3:0]=0001 Scale divider for MIPI /1

{0x3035, 0x11},

//[7:0]=56 PLL multiplier

{0x3036, 0x38},

//[4]=1 PLL root divider /2, [3:0]=1 PLL pre-divider /1

{0x3037, 0x11},

//[5:4]=00 PCLK root divider /1, [3:2]=00 SCLK2x root divider /1, [1:0]=01 SCLK root divider /2

{0x3108, 0x01},

//PLL2 configuration

//[5:4]=01 PRE_DIV_SP /1.5, [2]=1 R_DIV_SP /1, [1:0]=00 DIV12_SP /1

{0x303D, 0x10},

//[4:0]=11001 PLL2 multiplier DIV_CNT5B = 25

{0x303B, 0x19},

{0x3630, 0x2e},

{0x3631, 0x0e},

{0x3632, 0xe2},

{0x3633, 0x23},

{0x3621, 0xe0},

{0x3704, 0xa0},

{0x3703, 0x5a},

{0x3715, 0x78},

{0x3717, 0x01},

{0x370b, 0x60},

{0x3705, 0x1a},

{0x3905, 0x02},

{0x3906, 0x10},

{0x3901, 0x0a},

{0x3731, 0x02},

//VCM debug mode

{0x3600, 0x37},

{0x3601, 0x33},

//System control register changing not recommended

{0x302d, 0x60},

//??

{0x3620, 0x52},

{0x371b, 0x20},

//?? DVP

{0x471c, 0x50},

{0x3a13, 0x43},

{0x3a18, 0x00},

{0x3a19, 0xf8},

{0x3635, 0x13},

{0x3636, 0x06},

{0x3634, 0x44},

{0x3622, 0x01},

{0x3c01, 0x34},

{0x3c04, 0x28},

{0x3c05, 0x98},

{0x3c06, 0x00},

{0x3c07, 0x08},

{0x3c08, 0x00},

{0x3c09, 0x1c},

{0x3c0a, 0x9c},

{0x3c0b, 0x40},

//[7]=1 color bar enable, [3:2]=00 eight color bar

{0x503d, 0x00},

//[2]=1 ISP vflip, [1]=1 sensor vflip

{0x3820, 0x46},

//[7:5]=010 Two lane mode, [4]=0 MIPI HS TX no power down, [3]=0 MIPI LP RX no power down, [2]=1 MIPI enable, [1:0]=10 Debug mode; Default=0x58

{0x300e, 0x45},

//[5]=0 Clock free running, [4]=1 Send line short packet, [3]=0 Use lane1 as default, [2]=1 MIPI bus LP11 when no packet; Default=0x04

{0x4800, 0x14},

{0x302e, 0x08},

//[7:4]=0x3 YUV422, [3:0]=0x0 YUYV

//{0x4300, 0x30},

//[7:4]=0x6 RGB565, [3:0]=0x0 {b[4:0],g[5:3],g[2:0],r[4:0]}

{0x4300, 0x6f},

{0x501f, 0x01},

{0x4713, 0x03},

{0x4407, 0x04},

{0x440e, 0x00},

{0x460b, 0x35},

//[1]=0 DVP PCLK divider manual control by 0x3824[4:0]

{0x460c, 0x20},

//[4:0]=1 SCALE_DIV=INT(3824[4:0]/2)

{0x3824, 0x01},

//MIPI timing

// {0x4805, 0x10}, //LPX global timing select=auto

// {0x4818, 0x00}, //hs_prepare + hs_zero_min ns

// {0x4819, 0x96},

// {0x482A, 0x00}, //hs_prepare + hs_zero_min UI

//

// {0x4824, 0x00}, //lpx_p_min ns

// {0x4825, 0x32},

// {0x4830, 0x00}, //lpx_p_min UI

//

// {0x4826, 0x00}, //hs_prepare_min ns

// {0x4827, 0x32},

// {0x4831, 0x00}, //hs_prepare_min UI

//[7]=1 LENC correction enabled, [5]=1 RAW gamma enabled, [2]=1 Black pixel cancellation enabled, [1]=1 White pixel cancellation enabled, [0]=1 Color interpolation enabled

{0x5000, 0x07},

//[7]=0 Special digital effects, [5]=0 scaling, [2]=0 UV average disabled, [1]=1 Color matrix enabled, [0]=1 Auto white balance enabled

{0x5001, 0x03}

};

static u32 cfg_simple_awb[][2] =

{

// Disable Advanced AWB

{0x518d ,0x00},

{0x518f ,0x20},

{0x518e ,0x00},

{0x5190 ,0x20},

{0x518b ,0x00},

{0x518c ,0x00},

{0x5187 ,0x10},

{0x5188 ,0x10},

{0x5189 ,0x40},

{0x518a ,0x40},

{0x5186 ,0x10},

{0x5181 ,0x58},

{0x5184 ,0x25},

{0x5182 ,0x11},

// Enable simple AWB

{0x3406 ,0x00},

{0x5183 ,0x80},

{0x5191 ,0xff},

{0x5192 ,0x00},

{0x5001 ,0x03}

};

static u32 cfg_720p_60fps[][2] =

{//1280 x 720 binned, RAW10, MIPISCLK=280M, SCLK=56Mz, PCLK=56M

//PLL1 configuration

{0x3008, 0x42},

//[7:4]=0010 System clock divider /2, [3:0]=0001 Scale divider for MIPI /1

{0x3035, 0x21},

//[7:0]=70 PLL multiplier

{0x3036, 0x46},

//[4]=0 PLL root divider /1, [3:0]=5 PLL pre-divider /1.5

{0x3037, 0x05},

//[5:4]=01 PCLK root divider /2, [3:2]=00 SCLK2x root divider /1, [1:0]=01 SCLK root divider /2

{0x3108, 0x11},

//[6:4]=001 PLL charge pump, [3:0]=1010 MIPI 10-bit mode

{0x3034, 0x1A},

//[3:0]=0 X address start high byte

{0x3800, (0 >> 8) & 0x0F},

//[7:0]=0 X address start low byte

{0x3801, 0 & 0xFF},

//[2:0]=0 Y address start high byte

{0x3802, (8 >> 8) & 0x07},

//[7:0]=0 Y address start low byte

{0x3803, 8 & 0xFF},

//[3:0] X address end high byte

{0x3804, (2619 >> 8) & 0x0F},

//[7:0] X address end low byte

{0x3805, 2619 & 0xFF},

//[2:0] Y address end high byte

{0x3806, (1947 >> 8) & 0x07},

//[7:0] Y address end low byte

{0x3807, 1947 & 0xFF},

//[3:0]=0 timing hoffset high byte

{0x3810, (0 >> 8) & 0x0F},

//[7:0]=0 timing hoffset low byte

{0x3811, 0 & 0xFF},

//[2:0]=0 timing voffset high byte

{0x3812, (0 >> 8) & 0x07},

//[7:0]=0 timing voffset low byte

{0x3813, 0 & 0xFF},

//[3:0] Output horizontal width high byte

{0x3808, (1280 >> 8) & 0x0F},

//[7:0] Output horizontal width low byte

{0x3809, 1280 & 0xFF},

//[2:0] Output vertical height high byte

{0x380a, (720 >> 8) & 0x7F},

//[7:0] Output vertical height low byte

{0x380b, 720 & 0xFF},

//HTS line exposure time in # of pixels

{0x380c, (1896 >> 8) & 0x1F},

{0x380d, 1896 & 0xFF},

//VTS frame exposure time in # lines

{0x380e, (984 >> 8) & 0xFF},

{0x380f, 984 & 0xFF},

//[7:4]=0x3 horizontal odd subsample increment, [3:0]=0x1 horizontal even subsample increment

{0x3814, 0x31},

//[7:4]=0x3 vertical odd subsample increment, [3:0]=0x1 vertical even subsample increment

{0x3815, 0x31},

//[2]=0 ISP mirror, [1]=0 sensor mirror, [0]=1 horizontal binning

{0x3821, 0x01},

//little MIPI shit: global timing unit, period of PCLK in ns * 2(depends on # of lanes)

{0x4837, 36}, // 1/56M*2

//Undocumented anti-green settings

{0x3618, 0x00}, // Removes vertical lines appearing under bright light

{0x3612, 0x59},

{0x3708, 0x64},

{0x3709, 0x52},

{0x370c, 0x03},

//[7:4]=0x0 Formatter RAW, [3:0]=0x0 BGBG/GRGR

{0x4300, 0x00},

//[2:0]=0x3 Format select ISP RAW (DPC)

{0x501f, 0x03},

{0x3008, 0x02},

};Once the application SW has been completed we can create a system debug configuration which will download the programmable logic and start the application software running.

Running this application on the test hardware, gives the results as shown below

This example shows how an image processing application can be quickly created using the Vivado and Vitis.

This initial element of the design, has enabled us to demonstrate the selected development board and camera are capable of performing as desired.

If we were developing a custom board, this stage would have demonstrated the custom hardware was capable of performing as required. Demonstrating a significant risk retired early in the development process.

You can find the example design used in this project here

Now we have tested out the underlying hardware our next step is to develop the algorithms which we want to use on the deployed target.

Comments

Please log in or sign up to comment.