Hardware components | ||||||

|

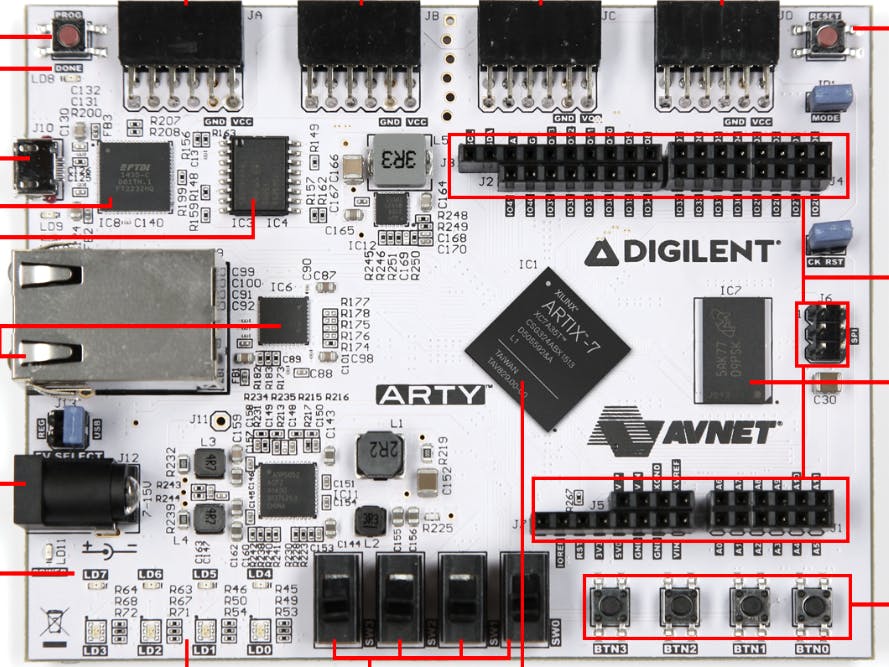

| × | 1 | |||

|

| × | 1 | |||

Software apps and online services | ||||||

|

| |||||

| ||||||

| ||||||

This project is used for communication system (radio). Carrier frequencies or modulation types can be changed without inserting new physical components.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_unsigned.ALL;

entity FSK_main is

Port ( clk, reset : in STD_LOGIC;

mt : in STD_LOGIC_VECTOR (7 downto 0);

dout : out STD_LOGIC_VECTOR (7 downto 0));

end FSK_main;

architecture Behavioral of FSK_main is

component clk_divider is

Port ( clk_in, reset : in STD_LOGIC;

divide_by : in STD_LOGIC_VECTOR (27 downto 0);

clk_out : out STD_LOGIC);

end component;

signal clk_high : std_logic;

signal clk_low : std_logic;

signal s1 : std_logic_vector(7 downto 0);

signal s2 : std_logic_vector(7 downto 0);

signal index : std_logic_vector(3 downto 0);

signal count_2 : std_logic_vector(5 downto 0);

signal s_count : std_logic_vector(2 downto 0);

type matrix is array(63 downto 0) of std_logic_vector(7 downto 0);

signal sinrom : matrix;

begin

sinrom <= ("01111110", "10001011", "10010111", "10100011", "10101111", "10111011", "11000101", "11001111", "11011001", "11100001", "11101001", "11101111", "11110100", "11111001", "11111100", "11111110", "11111110", "11111110", "11111100", "11111001", "11110100", "11101111", "11101001", "11100001", "11011001", "11001111", "11000101", "10111011", "10101111", "10100011", "10010111", "10001011", "01111110", "01110010", "01100101", "01011001", "01001101", "01000010", "00110111", "00101101", "00100100", "00011011", "00010100", "00001101", "00001000", "00000100", "00000001", "00000000", "00000001", "00000000", "00000001", "00000100", "00001000", "00001101", "00010100", "00011011", "00100100", "00101101", "00110111", "01000010", "01001101", "01011001", "01100101", "01110010");

process(clk_low,reset)

-- variable count_2 : std_logic_vector(5 downto 0);

-- variable s_count : std_logic_vector(2 downto 0);

begin

if reset = '1' then

s2 <= sinrom(0);

count_2 <= "000000";

s_count <= "000";

elsif rising_edge(clk_low) then

s2 <= sinrom(conv_integer(count_2));

count_2 <= count_2 + 1;

if falling_edge(count_2(5)) then

s_count <= s_count + 1;

if falling_edge(s_count(2)) then

index <= index + 1;

end if;

end if;

end if;

end process;

process(clk_high,reset)

variable count_1 : std_logic_vector(5 downto 0);

begin

if reset = '1' then

s1 <= sinrom(0);

count_1 := "000000";

elsif rising_edge(clk_high) then

s1 <= sinrom(conv_integer(count_1));

count_1 :=count_1 + 1;

end if;

end process;

Inst_clk_divider_1: clk_divider PORT MAP(clk, reset, x"0000186", clk_low);

Inst_clk_divider_2: clk_divider PORT MAP(clk, reset, x"0000062", clk_high);

dout <= s1 when mt(conv_integer(index)) = '1' and index(3) = '0' else

s2 when mt(conv_integer(index)) = '0' and index(3) = '0' else

"01111110";

end Behavioral;

Sinc implementation on the fpga

VHDLIt generates sinc function and sends to DAC(digital analog converter) to observe at the oscilloscope.

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity simple_clock_divider is

port( clk_in: in std_logic;

clk_out_divided: buffer std_logic;

clk_out_original : out std_logic;

sin_out:out std_logic_vector(7 downto 0) );

end entity;

architecture logic_flow of simple_clock_divider is

type matrix is array(0 to 255) of integer range 0 to 255;

signal sinrom : matrix;

signal count: natural range 1 to 50000;

signal count2: natural range 0 to 255;

signal temp_clk_out: std_logic:='0';

begin

sinrom <= (102,101,100, 99 ,98 ,98 ,97 ,97 ,98 ,98 ,99 ,100, 101, 103, 104, 105 ,107, 107, 108, 108, 108 ,108 ,107 ,106 ,105 ,103, 102, 100, 99, 98, 97, 96, 96, 96, 97 ,98 ,99 ,100 ,102 ,104 ,106, 107, 108, 109, 110, 110, 110, 109, 108, 106, 104, 102, 100, 99, 97, 95 ,94 ,94 ,94 ,94 ,95 ,97 ,98 ,101 ,103, 106 ,108 ,110, 112, 113, 113 ,113 ,113 ,111 ,109 ,107 ,104, 101, 98 ,95 ,92, 90,89 ,88 ,89 ,90, 92, 94,98 ,101 ,106 ,110 ,114 ,117 ,120 ,122, 122, 122, 120, 117, 113, 108, 102, 96, 90, 84, 78, 74 ,70, 69, 69 ,72, 77, 84, 94, 106, 119 ,134 ,150 ,167, 183, 199, 214, 228 ,239 ,248 ,254, 255 ,255,254, 248 ,239 ,228 ,214, 199, 183, 167, 150, 134 ,119,106, 94, 84, 77, 72, 69 ,69, 70 ,74, 78,84, 90 ,96, 102, 108, 113, 117, 120, 122 ,122, 122, 120 ,117, 114 ,110, 106 ,101, 98, 94, 92 ,90, 89, 88, 89 ,90 ,92 ,95, 98 ,101 ,104 ,107, 109, 111, 113, 113, 113, 113, 112 ,110 ,108, 106, 103 ,101 ,98, 97 ,95 ,94, 94 ,94 ,94, 95 ,97, 99 ,100, 102, 104 ,106 ,108, 109, 110 ,110, 110, 109, 108, 107, 106, 104, 102, 100, 99, 98, 97, 96 ,96 ,96, 97, 98, 99, 100, 102, 103 ,105 ,106, 107, 108, 108, 108, 108 ,107 ,107, 105, 104 ,103 ,101, 100, 99, 98, 98 ,97, 97, 98, 98, 99, 100, 101, 102);

clk_out_original <= clk_in;

process(clk_in)

begin

if (rising_edge(clk_in)) then

count <= count + 1;

if(count=50000) then

temp_clk_out<=not temp_clk_out;

count<=1;

end if;

end if;

end process;

clk_out_divided <= temp_clk_out;

process(clk_out_divided)

begin

if (rising_edge(clk_out_divided)) then

sin_out<= conv_std_logic_vector( sinrom(count2),8 );

if(count2=255) then

count2<=0;

end if;

count2 <= count2 + 1;

end if;

end process;

end architecture;

clear all;clc;

data=[1 1 1];

data1=[1 1 1];

f=1;

fa=4;

T=1/f;

Ts=1/16;

b=2*pi*f;

a=2*pi;

n=-128:127;

t=n*Ts;

beta=1/2;

for i=1:length(t)

sinc(i)=sin(pi*t(i))/(pi*t(i));

if n(i)==0

sinc(i)=1;

end

end

% sinc=round((sinc-min(sinc))/(max(sinc)-min(sinc))*255);

n=-256:255;

t=n*Ts;

data_src_top=zeros(1,length(n));

for i=1:length(data);

for j=1:256;

data_src_top(j+i/Ts)=data_src_top(j+i/Ts)+data(i)*sinc(j);

end

end

data_src_bottom=zeros(1,length(n));

for i=1:length(data);

for j=1:256;

data_src_bottom(j+i/Ts)=data_src_bottom(j+i/Ts)+data1(i)*sinc(j);

end

end

newn=-length(data_src_top)/2:length(data_src_top)/2-1;

newt=newn*Ts;

data_src_top_f=sin(2*pi*fa*newt).*data_src_top;

data_src_bottom_f=cos(2*pi*fa*newt).*data_src_bottom;

data_src_tot=data_src_top_f+data_src_bottom_f;

figure(1)

plot(data_src_top_f,'g')

figure(2)

plot(data_src_bottom_f,'k')

figure(3)

plot(data_src_tot,'m')

Comments