Ultra96 board it’s a low cost development platform for ARM-based architecture Zynq Ultrascale+. Ultra96 is based on the Linaro 96 boards so it has a big offer of daughter boards.

One of the most popular daughter boards for 96boards family is AVNET’s click Mezzanine. This daughter board allow to connect to ultra96 up to 2 click modules from Mikroe.

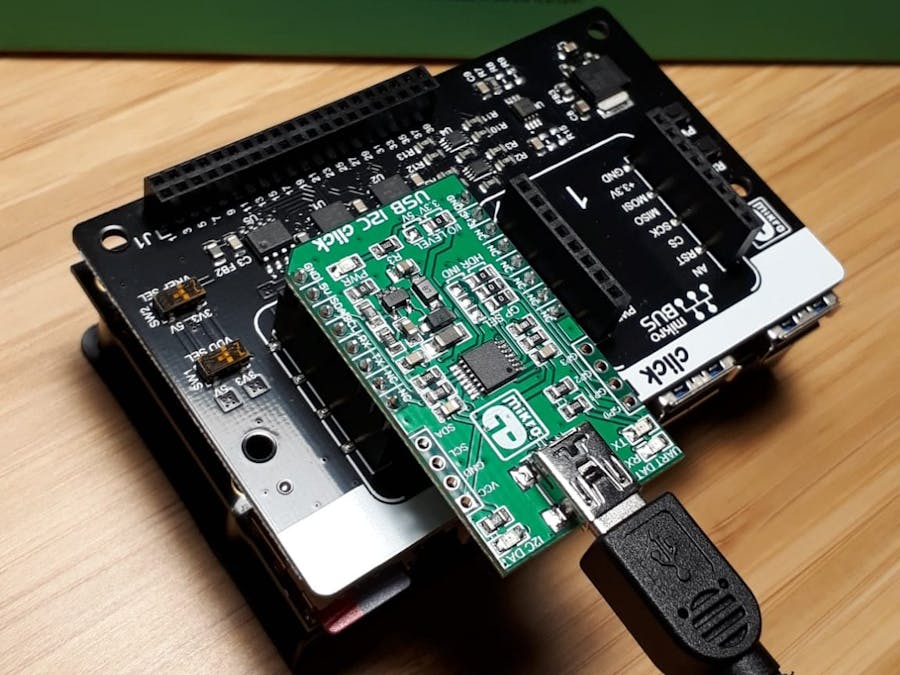

In this tutorial, we will to connect the USB I2C Click board, available with click mezzanine starter kit, to our ultra96, and we will manage it from petalinux.

This board bring us a bridge between USB and LVTTL UARTcommunication, so the idea of this tutorial is, first of all from Vivado, create the project and the block diagram for our design. Next, configure and build our customized version of Petalinux, and finally, test our development.

Creating the project and the block diagram.We have to open Vivado and create a new project, in my case, named ultra96_plnx_usbuart. When vivado ask us about the device, we have to click in “Boards” and select Ultra96 Evaluation Platform or Ultra96v2 Evaluation Platform, according the version of your Ultra96 board. If Ultra96 board does not appear, probably you have not the board file installed for this platform, so you have to go to AVNET’s GitHub repository, download the board files for Ultra96 board, and paste it in [Vivado install dir]/data/boards/board_files, then restart Vivado and the platform you added will be appear in this screen.

Once the project is created, we have to create a new block design, in my case named u96_bd_click_usbuart. The first element that we have to add to our diagram is the Zynq processing system. Now we have tho choices for communicate the processing system with the USB I2C click board.

_Through EMIO, we can redirect the native UART port of the ARM, through the PL to pins._We can add an axi peripheral to manage the UART communication and communicate it with the ARM by AXI protocol.

In this case, we will choose the second one, but the first one is also a valid option. One the project is open, we have to create a block design an name it, in my case, my block design is u96_bd_usbuart. Inside the block design we have to add a Zynq US+ processing system, and an axi_uartlite. Once 2 elements are in our design, click in Run Block Automation, and later, Run Connection Automation. Don’t forget connect the line pl_clk0to maxihpm0_fpd_aclkand maxihpm1_fpd_aclk. Also, the line pl_ps_irq must be connected to the interrupt port of axi_uartlite. If the interrupt port has no connection, the design will syntesized and implemented correctly, but Petalinux can’t will find the UARTport. Once all conections are done, it’s interesting click on Regenerate Layout, and Validate design, for ensure all in our design is correct.

Next step is create the HDL wrapper by right click over the block design in Sources window and click in Create HDL Wrapper. Then, click over Run Synthesis and wait. Once the process is done, we have to configure the ports. For that we need to open Synthesized Design and select the Layout I/O Planning.

On the bottom we can assign the pins for TX and RX signals.

Then click in Generate bitstream, saving the constraints and when the bitstream process is completed, next step is export the hardware project by click in File > Export > Export hardware, then we can close Vivado.

Building Petalinux.For this step, is necessary a Linux machine, virtual or physical. Once we are in Linux environment, is necessary download and install petalinux from Xilinx webpage. Notice thet the version of Petalinux has to be the same as the Vivado. Once we have the Petalinux SDK Installed, open the terminal and first we will add the petalinux variables to PATH by typing.

source <path-to-installed-PetaLinux>/settings.sh

Next we will create a petalinux project.

petalinux-create –-type project –-template zynqMP –-name plnx_click_usbuart

when the project has created, we have configure the petalinux distribution. In out case, we have to enable the new uart port, and install the drivers for axi_uartlite peripheral. For do this, we will type.

petalinux-config –-get-hw-description <path to project.sdk folder>

then we have to change the primary uart port.

Subsystem AUTO hardware Settings > Serial Settings > Primary stdin/stdout (psu_uart_1)

This is because the ultra96 boards has connected to the JTAG POD the port psu_uart_1, despite of the psu_uart_0. Then we have to exit of the configuration by select Exit and Save the configuration.

Next step is install the drivers for axi_uartlite peripheral. For that we have to configure the petalinux kernel. This action is not necessary because by default, uartlite drivers are enabled, but if you want to know where can be disable/enable

petalinux-config -c kernel

The a window similar to the last ones will appear, and the route for enable/disable drivers for uart lite is

Device Drivers > Character devices > Serial drivers > Xilinx uartlite serial port support

At this point, the last step is buil our linux distribution. For that we have to type

petalinux-build

After few minutes, our linux distribution will be built and we have to generate the images for the SD card. We have to go to the outputs folder.

cd <petalinux project folder>/images/linux

And type the next command

petalinux-package --boot --fsbl <fsbl_image> --fpga system.bit --uboot

This command will generate 2 files, BOOT.bin and image.ub. This files have to be copied in a SD card and inserted in Ultra96 boards. Then we have to connect our click mezzanine 96boards, the USB I2C click in slot number 2, and the JTAG POD. Once we have all connected, we can power on the Ultra96.

Inside Petalinux.The linux distribution will start and the consoles will show us what is happening in our board. Once the start process finish, we can see the peripherals

ls /dev

Then, a peripheral named ttyUL1 appear.

For send data throug our USB I2C click board we have to type

echo <frame> > ttyUL1

and the frame will be sended.

Thats all folks! For more information, my contact is pablo@controlpaths.com

Comments

Please log in or sign up to comment.