Hardware components | ||||||

|

| × | 1 | |||

| × | 1 | ||||

|

| × | 1 | |||

| × | 1 | ||||

| × | 1 | ||||

| × | 1 | ||||

| × | 1 | ||||

| × | 1 | ||||

Software apps and online services | ||||||

|

| |||||

| ||||||

Newtonian physics describe the behavior or very large bodies/particles within our universe. With certain assumptions, the laws can be applied to bodies/particles ranging from astronomical size to a golf ball (and even smaller), The interactions between different particle are governed by the following equation of gravity.

In an N-particle system, each particle experiences a force by other (N-1) particle. The result of the combined sum of forces result in acceleration of the said particle. Similarly, all other (N-1) particle experience force from other particles in the system simultaneously. The resulting acceleration of all the particles, combined with initial position in space, initial velocity and time-step derive new position of all the N-particles respectively. For the sake of simplicity in implementation, the following assumptions are made:

1. All particles are point masses

2. G=1

3. Introduce a fudge factor in gravity calculations toavoid errors when two point masses are at exactly same co-ordinates.

The design has been implemented to enable user to load initial co-ordinates, mass, a "softening factor" and simulation time-step in 16b signed integer format through python software. Although floating point add, subtract and multiply is provided by Vivado environment, an effort was put to design these for custom floating point format.

Design: Proof of ConceptThe algorithm was implemented and simulated using python software, The following is the main algorithm and screen capture of the particle simulation performed on PC before the hardware implementation was carried out.

This algorithm has a computational complexity of N**2 due to iterative process. This is a great opportunity for implementing an accelerator in hardware. You can try nbody_x86.py to see how slow the particle simulation is running in just software. The particle simulation will run much faster with accelerators implemented in hardware.

This algorithm can be vectorized, hence reducing the complexity to O(N) if a vector processor is used. The below example is to identify the critical portions of algorithm that are compute intensive and provide accelerator for them in fabric/PL.

Let’s say at time t0, all the particles’ information of position and velocity are known.

Consider 2 particle system. The acceleration on 1st particle due to 2nd particle is calculated as follows:

a =(G * m2)/r**2

To preserve the directional information of acceleration: a = (G * m2*|r|)/r**3

NBody problem:

1. The above concept can be extended to N body system.

2. In GRAPE-6 [x], a softening factor“ε” was used to study detailed effects of size. For this project, is was set to 0.

3. Another softening factor was used to prevent different particles from coming extremely close to each other, i.e. to prevent “r~=0”, as shown by the variable "sf" in above python software.

Hardware DesignThe design incorporates 8 parallel accelerator engines that can completely support up to 4000 bodies!

Implementation with 8 Parallel Accelerators

The original design had 1 accelerator running at 75 MHz. Addition of 7 more accelerators in parallel and more than doubling the operating frequency increased power consumption by about 1 W. Data for 1 accelerator is shown in a later section. Data for 8 parallel accelerators is given in this table here.

Performance

Design meets timing at 200 MHz for 4000 particles! Floating point add and multiply have been modified by adding pipelines.

Implementation with Just 1 Accelerator at 200MHz - Data for Comparison

In spite of the complex logic, The implementation consumes the following resources on XCZU3EG with a single gravity compute engine. One gravity engine can compute interactions between 1024 particles (dictated by the depth of input and output BRAMs). The timing was successfully closed at 200 MHz. Pipelining was implemented in the gravity engine. Reset pipelining was implemented in each local module to optimize global reset propagation routing. Entire design runs on a single clock source.

Floating Point Arithmetic

As the numbers in scientific computations range from small extremes to astronomically large values, IEEE754 FP32 was the initial choice of floating point arithmetic. In IEEE754 FP32, numbers are represented by 1 sign bit, 8 exponent bits and 23 mantissa bits as shown in the figure:

However, DSP48E2 can perform only 27bx18b multiplications. Thus, a choice was made to use a custom floating point representation with only 18 mantissa bits. Thus, the floating point arithmetic in this design uses 27b floating point representation.

Smallest number that can be represented in this format: +/- 1.000000000000000001 x 2**(-126)

Largest number that can be represented in this format: +/- 1.111111111111111111 x 2**(127)

Bias of the exponent is 127

The IEEE 754 conditions of NaN, Overflow, and Underflow have not been implemented to the fullest extent.

Implemented FP Arithmetic

IPI based Floating point arithmetic was implemented. Floating point add, multiply were customized to 27 bits for efficient use of DSP48 while floating point inverse square root was fixed to single precision floating point notation due to customization limits. Int16 to floating point, floating point to int16 was also done using Xilinx IPs.

Flow Diagram

The following figure shows a top level view of RAMs, compute engine, pipelined gravity engine, etc.

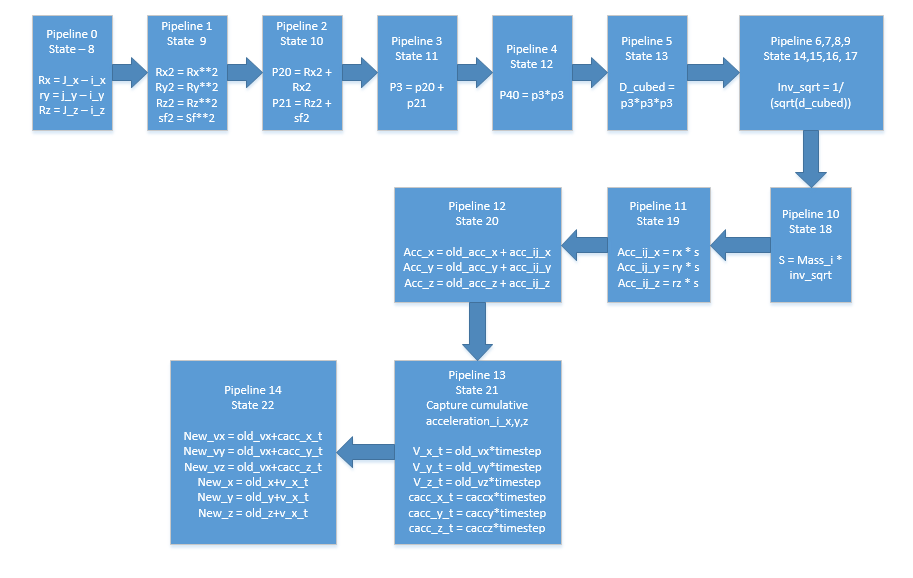

Gravity Engine

The gravity engine is the core of the design. It is implemented as per the algorithm shown in above diagram. The following diagram shows the implementation details of the gravity engine and all the 15 pipelines.

Control and Status Registers; Address Spaces

All BRAMs are controlled using a BRAM controller developed in RTL based on APB3 bus. AXI -APB3 bridge was instantiated in block design. Similarly, an additional APB control and status register bank was implemented in order to control the compute engine. The following are address segments and register spaces:

Design Hierarchy

i_design_1 is the PS system and i_compute_engine is hardware design implemented in the PL part.

Software Flow

Python software was written on PYNQ framework to perform the following actions in sequence:

1. Calculate initial conditions of x, y, z, m of N particles in system, softening factor and simulation time step.

2. Configure the compute engine by loading the int16 x, y, z, m values into BRAMs

3. Start compute engine

4. Wait for compute engine to finish one time step

5. Retrieve the new x, y, z from TXRAMs

6. Create a DisplayPort frame using DisplayPort module. Zero the frame, load the frame with new data and write the frame to monitor.

7. Repeat!

DisplayPort was configured to 1280 x 720 pixels

The new positions of particles can be well beyond monitor size.They are just not shown.

Step 1: Build the FPGA Bitstream from Provided Source FilesThis step may take 45 min to a couple hours, depending on how fast your computer is when running Vivado. The compute time for building is because we are going for high performance with 8 parallel accelerators at 200 MHz.

If you would like to skip this build step, you can use the provided nbodypynq.bit and nbodypynq.tcl from the attachments section.

1. Create a directory on your machine, which we will refer to as <workspace>.

2. Create directory "src" in <workspace>.

3. Download all source files and place them in "src" directory.

4. Open Vivado 2018.3.

5. In the Vivado TCL console

a. cd <workspace>

b. source./src/nbody.tcl

6. Wait for the bitstream to be generated. This may take 45 min to a few hours, depending on your machine. The Vivado project will be in <workspace>/nbody

7. The necessary files to be loaded onto the Ultra96 will be in

<workspace>/nbody/pynq_overlay_files/ and<workspace>/src/nbody.ipynb

Step 2: Set Up the Ultra96 Board1. Download the PYNQ image for Ultra96 from www.pynq.io/board.html

2. Put that PYNQ image on your micro SD card by following the instructions at https://pynq.readthedocs.io/en/latest/appendix.html#writing-the-sd-card and put the micro SD card in the slot on the Ultra96. Make sure it is inserted fully.

3. Plug in your Display Port monitor into the Ultra96 board using the mini Display Port connector. Make sure the monitor is at least 1280 x 720 resolution.

4. (Optional) Plug in a USB mouse and USB keyboard into the USB ports of the Ultra96 board.

5. Follow the USB cable (preferred) or WiFi connection methods in this video for setting up PYNQ on the Ultra96:

6. With the board turned on and connected to your computer, refer to https://ultra96-pynq.readthedocs.io/en/latest/getting_started.html#accessing-files-on-the-board for how to access the files on the Ultra96.

a. If you are connecting the board to your computer via the micro USB cable (USB Ethernet, preferred method), \\PYNQ refers to \\192.168.3.1

b. If you are connecting the board to your computer via WiFi, \\PYNQ refers to \\192.168.2.1

7. Create directories named "nbody-single" and“nbody-parallel” in \\PYNQ\xilinx\pynq\overlays\

8. Copy the files (nbodypynq.bit, nbodyoverlay.tcl) from <workspace>/nbody/pynq_overlay_files/ to \\PYNQ\xilinx\pynq\overlays\nbody-single\ or nbody-parallel, depending on if you have defined PARALLEL in vars.vh. The provided vars.vh is the nbody-parallel configuration.

9. Create a directory named "nbody" in \\PYNQ\xilinx\jupyter_notebooks\

10. Copy Jupyter notebook <workspace>/src/nbody.ipynb to \\PYNQ\xilinx\jupyter_notebooks\nbody\

Step 3: Use the Jupyter Notebook to Run the Particle SimulationA PYNQ Desktop should be displayed on the Display Port monitor attached to the Ultra96, with a “Welcome to PYNQ” getting started page open in the Chromium browser. You have the option to interact with the Ultra96 board using the mouse and keyboard (if you plugged those into the Ultra96) in the Chromium browser to use the Jupyter notebooks. You may find it easier to use the Jupyter notebooks from your computer that is connected to the Ultra96 over the microUSB cable.

1. In a web browser, navigate to the nbody Jupyter notebook by going to the IP address for connecting to the board (e.g.192.168.3.1). When connecting from another computer, you may be asked for a password. It’s “xilinx", all lowercase with no quotation marks.

For more information on connecting to the Pynq Jupyter notebooks please refer to https://ultra96-pynq.readthedocs.io/en/latest/getting_started.html#connecting-to-jupyter-notebooks

2. Update the line:

overlay =Overlay("…")

to point to the desired overlay (e.g. /home/xilinx/pynq/overlays/nbody-parallel/nbodypynq.bit if vars.vh had PARALLEL defined)

3. Click on the step with all the code and click the Run button to run it.

Wait a about 10 seconds. Then, you will see the monitor go dark for about 5 seconds and the particle simulation will run for about 45 seconds. (During this time, the mouse & keyboard attached to the Ultra96 will not work) All bodies with mass < average of all masses are colored in white and others in red.(You can ignore the HWH file warning that appears in the Jupyter notebook window)

4. Try setting initial_condition to 1, 2, and 3 and running again in the Jupyter notebook to see different particle simulations displayed

5. When you are done, be sure to shut down theUltra96 properly, to avoid corrupting the root file system. One way to do this is to open a terminal fromthe browser in the Jupyter Notebooks area, or refer to https://ultra96-pynq.readthedocs.io/en/latest/getting_started.html#opening-a-usb-serial-terminal

Enter the command “shutdown -h now” and let theboard do a clean shutdown.

Modifications to Hardware Design That You Can Try

A. If `define PARALLEL is commented out in <workspace>/src/vars.vh, a single compute engine is implemented. Otherwise, 8 parallel compute engines are implemented in hardware, utilizing more PL resources. You could compare parallel vs. single implementations.

B. Max. number of particles could be changed in <workspace>/src/vars.vh. However, the device meets timing with max. particles of up to 4000, at 200 MHz clock frequency. If more particles are required, the clock frequency must be reduced and timing closure becomes difficult as utilization skyrockets. You would need to widen the address bus to increase the number of particles to 8000 or 16000

C. If execute units number is changed, final stages of the pipelines in parallel_gravity_accelerator needs to be manually modified.

Verilog Simulation for Hardware Development

1. Two testbenches are provided

(a) testbench.v

(b) testbench_fp_arithmetic.v

2. These can be added to the Vivado project and to do circuit simulation of any hardware design modifications you make

3. To save time, modify nbody.tcl to build the project only and not generate bitstream.

- nbody_x86.py Python implementation of N-body particle simulation

- nbodypynq.bit Pre-built bitstream for Pynq overlay

- nbodypynq.tcl Pre-built TCL script for Pynq overlay

- apb3_bram_cntrl.v

- apb3_regbank.v

- compute_engine.v

- design_1.tcl

- Apache 2.0 license

- design_fixed_to_float.tcl

- design_float_to_fixed.tcl

- design_fp_add.tcl

- design_fp_invsqrt.tcl

- design_fp_mult.tcl

- gravity_accelerator.v

- nbody.ipynb Jupyter Notebook

- nbody.tcl

- nbody.xdc

- parallel_gravity_accelerator.v

- reset_pipe.v

- testbench.v

- testbench_fp_arithmetic.v

- top.v

- vars.vh

- xilinx_simple_dual_port_1_clock_ram.v

- xlnx_tdpram_macro.v

- design_1_wrapper.v

nbody_x86.py Python implementation of N-body particle simulation

Python##########################################################################

# Copyright 2019 Xilinx

#

# Licensed under the Apache License, Version 2.0 (the "License");

# you may not use this file except in compliance with the License.

# You may obtain a copy of the License at

#

# http://www.apache.org/licenses/LICENSE-2.0

#

# Unless required by applicable law or agreed to in writing, software

# distributed under the License is distributed on an "AS IS" BASIS,

# WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

# See the License for the specific language governing permissions and

# limitations under the License.

#

##########################################################################

#

# 4/4/2019 - Rajeev Patwari

#

# N-Body simulations

# Software to simulate N-body interactions based on Newtonian Gravity

# calculations. The system is confined to point mass bodies with some

# limitations

# This simulation is inspiration to design FPGA accelerator

# Testcase#1 shows why FPGA parallel acceleration is required!

#

# References:

# 1. http://cc.doc.ic.ac.uk/projects/prj_axel/nbody.html

#

# SW installations: Anaconda with Python 3.7 from here

# https://www.anaconda.com/distribution/

#

##########################################################################

import numpy as np

import matplotlib.pyplot as plt

import matplotlib.animation as animation

import mpl_toolkits.mplot3d.axes3d as p3

import random

import math

# ----------- configure before run - begin

# select a test case between 1 and 10

# uncomment one of the following

#testcase = 1 # n=500; very slow on pc - this is why we need accelerator!

testcase = 2 # n=2

#testcase = 3 # n=12

#testcase = 4 # n=3

#testcase = 5 # n=500; very slow on PC

#testcase = 6 # n=500; very slow on PC

#testcase = 7 # n=500; very slow on PC

# ----------- configure before run - end

# Fixing random state for reproducibility

random.seed(19680801)

# initialize particle positions, mass and initial velocity

graphlim = 4000

numparticles = 500

timestep = np.float(100)

if testcase==1:

x = list(np.random.uniform(-3000,3000,numparticles))

y = list(np.random.uniform(-3000,3000,numparticles))

z = list(np.random.uniform(-3000,3000,numparticles))

mass = list(np.random.uniform(100,110,numparticles))

vx = list(np.random.uniform(0,0,numparticles ))

vy = list(np.random.uniform(0,0,numparticles ))

vz = list(np.random.uniform(0,0,numparticles ))

mass[0] = 100

sf = 4000.0

elif testcase==2:

x = [300, -300]

y = [0,0]

z = [0,0]

mass = [295, 300]

vx = [-0.1,0]

vy = [0.1,0]

vz = [0,0]

sf = 600.0

numparticles = 2

elif testcase==3:

numparticles = 12

x = [100, 100, -100,-100, 100, 100, -100,-100, 100, 100, -100,-100]

y = [100, -100, 100, -100,100, -100, 100, -100, 100, -100, 100, -100]

z = [0, 0, 0, 0, 100, 100, 100, 100, -100,-100, -100, -100]

mass = [0.5 for i in range(0,numparticles,1)]

vx = [0.0 for i in range(0,numparticles,1)]

vy = [0.0 for i in range(0,numparticles,1)]

vz = [0.0 for i in range(0,numparticles,1)]

sf = 200.0

elif testcase==4: # 2 planets trying to orbit a star

numparticles = 3

x = [0, 0, 10]

y = [0, 25, 10]

z = [0, 0, 0 ]

mass = [10, 10, 5]

vx = [0.0, 0.0, 0.0]

vy = [0.0, 0.0, 0.0 ]

vz = [0.0, 0.0, 0.0]

sf = 2

graphlim = 800

timestep = np.float(1)

elif testcase==5:

lim = 3000.0/2

x = list(lim*np.random.random_sample((numparticles,)))

y = list(lim*np.random.random_sample((numparticles,)))

z = list(lim*np.random.random_sample((numparticles,)))

mass = list(3000*np.random.random_sample((numparticles,)))

vx = list(np.random.uniform(-1,1,numparticles ))

vy = list(np.random.uniform(-1,1,numparticles ))

vz = list(np.random.uniform(-1,1,numparticles ))

mass[0] = 100

sf = 4000.0

graphlim = 8000

elif testcase==6:

radius, h_max, v_max = 1000, 1280, 720

theta = np.linspace(0, 2*np.pi, numparticles)

a, b = 1 * np.cos(theta), 1 * np.sin(theta)

r = np.random.rand((numparticles))

x, y = radius*r * np.cos(theta), radius*r * np.sin(theta)

x = [int(i+640) for i in x]

y = [int(i+360) for i in y]

mass = [random.randint(10, 110) for i in range(0, numparticles)]

z = [0 for i in range(0, numparticles)]

#x[0], y[0], mass[0] = 640, 360, 10000

vx = [0 for i in range(0, numparticles)]

vy = [0 for i in range(0, numparticles)]

vz = [0 for i in range(0, numparticles)]

sf = 300.0

timestep = np.float(5)

graphlim = 1500

else:

print ("Chose between 1 to 6 and re-run")

# Create new Figure with black background

fig = plt.figure()

ax = p3.Axes3D(fig)

# Add a subplot with no frame, set limits

ax.set_xlim3d(-graphlim, graphlim)

ax.set_ylim3d(-graphlim, graphlim)

ax.set_zlim3d(-graphlim, graphlim)

ax.set_xlabel('X Label')

ax.set_ylabel('Y Label')

ax.set_zlabel('Z Label')

print(len(x), len(y), len(z), len(vx), len(vy), len(vz), len(mass))

def update(*args):

""" can be parameerized if needed """

global x,y,vx,vy,mass,numparticles, sf

accx = [0.0 for i in range(0, numparticles)]

accy = [0.0 for i in range(0, numparticles)]

accz = [0.0 for i in range(0, numparticles)]

for i in range(0, numparticles, 1):

for j in range(0, numparticles, 1):

if (j!=i):

rx = x[j] - x[i]

ry = y[j] - y[i]

rz = z[j] - z[i]

dd = np.power(rx,2) + np.power(ry,2) + np.power(rz,2) + sf*sf

#print(np.power(dd,3))

d = 1/np.sqrt(np.power(dd,3))

s = mass[j]*d

accx[i] += rx*s

accy[i] += ry*s

accz[i] += rz*s

#print(accx[0], x[0])

x[i] += vx[i]*timestep

y[i] += vy[i]*timestep

z[i] += vz[i]*timestep

vx[i] += accx[i]*timestep

vy[i] += accy[i]*timestep

vz[i] += accz[i]*timestep

ax.clear()

ax.scatter(x,y,z,'.')

ax.set_xlim3d(-graphlim, graphlim)

ax.set_ylim3d(-graphlim, graphlim)

ax.set_zlim3d(-graphlim, graphlim)

ax.set_xlabel('X Label')

ax.set_ylabel('Y Label')

ax.set_zlabel('Z Label')

return

# Construct the animation, using the update function as the animation director.

anim = animation.FuncAnimation(fig, update, interval=10)

plt.show()

anim.save('nbody_pc_sim1.html')

#with np.errstate(over='ignore'):

nbodypynq.bit Pre-built bitstream for Pynq overlay

Plain textNo preview (download only).

nbodypynq.tcl Pre-built TCL script for Pynq overlay

Tcl##########################################################################

#

# Copyright 2019 Xilinx

#

# Licensed under the Apache License, Version 2.0 (the "License");

# you may not use this file except in compliance with the License.

# You may obtain a copy of the License at

#

# http://www.apache.org/licenses/LICENSE-2.0

#

# Unless required by applicable law or agreed to in writing, software

# distributed under the License is distributed on an "AS IS" BASIS,

# WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

# See the License for the specific language governing permissions and

# limitations under the License.

#

##########################################################################

################################################################

# This is a generated script based on design: design_1

#

# Though there are limitations about the generated script,

# the main purpose of this utility is to make learning

# IP Integrator Tcl commands easier.

################################################################

namespace eval _tcl {

proc get_script_folder {} {

set script_path [file normalize [info script]]

set script_folder [file dirname $script_path]

return $script_folder

}

}

variable script_folder

set script_folder [_tcl::get_script_folder]

################################################################

# Check if script is running in correct Vivado version.

################################################################

set scripts_vivado_version 2018.3

set current_vivado_version [version -short]

if { [string first $scripts_vivado_version $current_vivado_version] == -1 } {

puts ""

catch {common::send_msg_id "BD_TCL-109" "ERROR" "This script was generated using Vivado <$scripts_vivado_version> and is being run in <$current_vivado_version> of Vivado. Please run the script in Vivado <$scripts_vivado_version> then open the design in Vivado <$current_vivado_version>. Upgrade the design by running \"Tools => Report => Report IP Status...\", then run write_bd_tcl to create an updated script."}

return 1

}

################################################################

# START

################################################################

# To test this script, run the following commands from Vivado Tcl console:

# source design_1_script.tcl

# If there is no project opened, this script will create a

# project, but make sure you do not have an existing project

# <./nbody/nbodyproj.xpr> in the current working folder.

set list_projs [get_projects -quiet]

if { $list_projs eq "" } {

create_project nbodyproj nbody -part xczu3eg-sbva484-1-i

}

# CHANGE DESIGN NAME HERE

variable design_name

set design_name design_1

# If you do not already have an existing IP Integrator design open,

# you can create a design using the following command:

# create_bd_design $design_name

# Creating design if needed

set errMsg ""

set nRet 0

set cur_design [current_bd_design -quiet]

set list_cells [get_bd_cells -quiet]

if { ${design_name} eq "" } {

# USE CASES:

# 1) Design_name not set

set errMsg "Please set the variable <design_name> to a non-empty value."

set nRet 1

} elseif { ${cur_design} ne "" && ${list_cells} eq "" } {

# USE CASES:

# 2): Current design opened AND is empty AND names same.

# 3): Current design opened AND is empty AND names diff; design_name NOT in project.

# 4): Current design opened AND is empty AND names diff; design_name exists in project.

if { $cur_design ne $design_name } {

common::send_msg_id "BD_TCL-001" "INFO" "Changing value of <design_name> from <$design_name> to <$cur_design> since current design is empty."

set design_name [get_property NAME $cur_design]

}

common::send_msg_id "BD_TCL-002" "INFO" "Constructing design in IPI design <$cur_design>..."

} elseif { ${cur_design} ne "" && $list_cells ne "" && $cur_design eq $design_name } {

# USE CASES:

# 5) Current design opened AND has components AND same names.

set errMsg "Design <$design_name> already exists in your project, please set the variable <design_name> to another value."

set nRet 1

} elseif { [get_files -quiet ${design_name}.bd] ne "" } {

# USE CASES:

# 6) Current opened design, has components, but diff names, design_name exists in project.

# 7) No opened design, design_name exists in project.

set errMsg "Design <$design_name> already exists in your project, please set the variable <design_name> to another value."

set nRet 2

} else {

# USE CASES:

# 8) No opened design, design_name not in project.

# 9) Current opened design, has components, but diff names, design_name not in project.

common::send_msg_id "BD_TCL-003" "INFO" "Currently there is no design <$design_name> in project, so creating one..."

create_bd_design $design_name

common::send_msg_id "BD_TCL-004" "INFO" "Making design <$design_name> as current_bd_design."

current_bd_design $design_name

}

common::send_msg_id "BD_TCL-005" "INFO" "Currently the variable <design_name> is equal to \"$design_name\"."

if { $nRet != 0 } {

catch {common::send_msg_id "BD_TCL-114" "ERROR" $errMsg}

return $nRet

}

set bCheckIPsPassed 1

##################################################################

# CHECK IPs

##################################################################

set bCheckIPs 1

if { $bCheckIPs == 1 } {

set list_check_ips "\

xilinx.com:ip:axi_apb_bridge:3.0\

xilinx.com:ip:axi_uart16550:2.0\

xilinx.com:ip:clk_wiz:6.0\

xilinx.com:ip:proc_sys_reset:5.0\

xilinx.com:ip:zynq_ultra_ps_e:3.2\

"

set list_ips_missing ""

common::send_msg_id "BD_TCL-006" "INFO" "Checking if the following IPs exist in the project's IP catalog: $list_check_ips ."

foreach ip_vlnv $list_check_ips {

set ip_obj [get_ipdefs -all $ip_vlnv]

if { $ip_obj eq "" } {

lappend list_ips_missing $ip_vlnv

}

}

if { $list_ips_missing ne "" } {

catch {common::send_msg_id "BD_TCL-115" "ERROR" "The following IPs are not found in the IP Catalog:\n $list_ips_missing\n\nResolution: Please add the repository containing the IP(s) to the project." }

set bCheckIPsPassed 0

}

}

if { $bCheckIPsPassed != 1 } {

common::send_msg_id "BD_TCL-1003" "WARNING" "Will not continue with creation of design due to the error(s) above."

return 3

}

##################################################################

# DESIGN PROCs

##################################################################

# Procedure to create entire design; Provide argument to make

# procedure reusable. If parentCell is "", will use root.

proc create_root_design { parentCell } {

variable script_folder

variable design_name

if { $parentCell eq "" } {

set parentCell [get_bd_cells /]

}

# Get object for parentCell

set parentObj [get_bd_cells $parentCell]

if { $parentObj == "" } {

catch {common::send_msg_id "BD_TCL-100" "ERROR" "Unable to find parent cell <$parentCell>!"}

return

}

# Make sure parentObj is hier blk

set parentType [get_property TYPE $parentObj]

if { $parentType ne "hier" } {

catch {common::send_msg_id "BD_TCL-101" "ERROR" "Parent <$parentObj> has TYPE = <$parentType>. Expected to be <hier>."}

return

}

# Save current instance; Restore later

set oldCurInst [current_bd_instance .]

# Set parent object as current

current_bd_instance $parentObj

# Create interface ports

set APB_M [ create_bd_intf_port -mode Master -vlnv xilinx.com:interface:apb_rtl:1.0 APB_M ]

set APB_M2 [ create_bd_intf_port -mode Master -vlnv xilinx.com:interface:apb_rtl:1.0 APB_M2 ]

set APB_M3 [ create_bd_intf_port -mode Master -vlnv xilinx.com:interface:apb_rtl:1.0 APB_M3 ]

set gpio_sensors [ create_bd_intf_port -mode Master -vlnv xilinx.com:interface:gpio_rtl:1.0 gpio_sensors ]

set uart1 [ create_bd_intf_port -mode Master -vlnv xilinx.com:interface:uart_rtl:1.0 uart1 ]

# Create ports

set bt_ctsn [ create_bd_port -dir I bt_ctsn ]

set bt_rtsn [ create_bd_port -dir O bt_rtsn ]

set peripheral_reset [ create_bd_port -dir O -from 0 -to 0 -type rst peripheral_reset ]

set pl_clk1 [ create_bd_port -dir O -type clk pl_clk1 ]

set pl_clk2_300MHz [ create_bd_port -dir O -type clk pl_clk2_300MHz ]

set pl_clk3_374MHz [ create_bd_port -dir O -type clk pl_clk3_374MHz ]

set pll_locked [ create_bd_port -dir O pll_locked ]

set uart0_ctsn [ create_bd_port -dir I -type data uart0_ctsn ]

set uart0_rtsn [ create_bd_port -dir O -type data uart0_rtsn ]

set uart0_rxd [ create_bd_port -dir I uart0_rxd ]

set uart0_txd [ create_bd_port -dir O uart0_txd ]

# Create instance: axi_apb_bridge_0, and set properties

set axi_apb_bridge_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:axi_apb_bridge:3.0 axi_apb_bridge_0 ]

set_property -dict [ list \

CONFIG.C_APB_NUM_SLAVES {3} \

] $axi_apb_bridge_0

# Create instance: axi_uart16550_0, and set properties

set axi_uart16550_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:axi_uart16550:2.0 axi_uart16550_0 ]

set_property -dict [ list \

CONFIG.C_S_AXI_ACLK_FREQ_HZ {99999901} \

] $axi_uart16550_0

# Create instance: clk_wiz_0, and set properties

set clk_wiz_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:clk_wiz:6.0 clk_wiz_0 ]

set_property -dict [ list \

CONFIG.CLKIN1_JITTER_PS {400.0} \

CONFIG.CLKOUT1_DRIVES {BUFGCE} \

CONFIG.CLKOUT1_JITTER {175.029} \

CONFIG.CLKOUT1_PHASE_ERROR {222.305} \

CONFIG.CLKOUT1_REQUESTED_OUT_FREQ {200.000} \

CONFIG.CLKOUT2_DRIVES {BUFGCE} \

CONFIG.CLKOUT3_DRIVES {BUFGCE} \

CONFIG.CLKOUT4_DRIVES {BUFGCE} \

CONFIG.CLKOUT5_DRIVES {BUFGCE} \

CONFIG.CLKOUT6_DRIVES {BUFGCE} \

CONFIG.CLKOUT7_DRIVES {BUFGCE} \

CONFIG.FEEDBACK_SOURCE {FDBK_AUTO} \

CONFIG.MMCM_CLKFBOUT_MULT_F {48.000} \

CONFIG.MMCM_CLKIN1_PERIOD {40.000} \

CONFIG.MMCM_CLKIN2_PERIOD {10.0} \

CONFIG.MMCM_CLKOUT0_DIVIDE_F {6.000} \

CONFIG.MMCM_DIVCLK_DIVIDE {1} \

CONFIG.SECONDARY_SOURCE {Single_ended_clock_capable_pin} \

CONFIG.USE_PHASE_ALIGNMENT {true} \

CONFIG.USE_SAFE_CLOCK_STARTUP {true} \

] $clk_wiz_0

# Create instance: proc_sys_reset_0, and set properties

set proc_sys_reset_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:proc_sys_reset:5.0 proc_sys_reset_0 ]

# Create instance: proc_sys_reset_1, and set properties

set proc_sys_reset_1 [ create_bd_cell -type ip -vlnv xilinx.com:ip:proc_sys_reset:5.0 proc_sys_reset_1 ]

# Create instance: ps8_0_axi_periph, and set properties

set ps8_0_axi_periph [ create_bd_cell -type ip -vlnv xilinx.com:ip:axi_interconnect:2.1 ps8_0_axi_periph ]

set_property -dict [ list \

CONFIG.NUM_MI {2} \

] $ps8_0_axi_periph

# Create instance: zynq_ultra_ps_e_0, and set properties

set zynq_ultra_ps_e_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:zynq_ultra_ps_e:3.2 zynq_ultra_ps_e_0 ]

set_property -dict [ list \

CONFIG.CAN0_BOARD_INTERFACE {custom} \

CONFIG.CAN1_BOARD_INTERFACE {custom} \

CONFIG.CSU_BOARD_INTERFACE {custom} \

CONFIG.DP_BOARD_INTERFACE {custom} \

CONFIG.GEM0_BOARD_INTERFACE {custom} \

CONFIG.GEM1_BOARD_INTERFACE {custom} \

CONFIG.GEM2_BOARD_INTERFACE {custom} \

CONFIG.GEM3_BOARD_INTERFACE {custom} \

CONFIG.GPIO_BOARD_INTERFACE {custom} \

CONFIG.IIC0_BOARD_INTERFACE {custom} \

CONFIG.IIC1_BOARD_INTERFACE {custom} \

CONFIG.NAND_BOARD_INTERFACE {custom} \

CONFIG.PCIE_BOARD_INTERFACE {custom} \

CONFIG.PJTAG_BOARD_INTERFACE {custom} \

CONFIG.PMU_BOARD_INTERFACE {custom} \

CONFIG.PSU_BANK_0_IO_STANDARD {LVCMOS18} \

CONFIG.PSU_BANK_1_IO_STANDARD {LVCMOS18} \

CONFIG.PSU_BANK_2_IO_STANDARD {LVCMOS18} \

CONFIG.PSU_BANK_3_IO_STANDARD {LVCMOS18} \

CONFIG.PSU_DDR_RAM_HIGHADDR {0x7FFFFFFF} \

CONFIG.PSU_DDR_RAM_HIGHADDR_OFFSET {0x00000002} \

CONFIG.PSU_DDR_RAM_LOWADDR_OFFSET {0x80000000} \

CONFIG.PSU_IMPORT_BOARD_PRESET {} \

CONFIG.PSU_MIO_0_DIRECTION {inout} \

CONFIG.PSU_MIO_0_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_0_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_0_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_0_SLEW {slow} \

CONFIG.PSU_MIO_10_DIRECTION {inout} \

CONFIG.PSU_MIO_10_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_10_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_10_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_10_SLEW {slow} \

CONFIG.PSU_MIO_11_DIRECTION {inout} \

CONFIG.PSU_MIO_11_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_11_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_11_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_11_SLEW {slow} \

CONFIG.PSU_MIO_12_DIRECTION {inout} \

CONFIG.PSU_MIO_12_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_12_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_12_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_12_SLEW {slow} \

CONFIG.PSU_MIO_13_DIRECTION {inout} \

CONFIG.PSU_MIO_13_DRIVE_STRENGTH {4} \

CONFIG.PSU_MIO_13_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_13_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_13_SLEW {slow} \

CONFIG.PSU_MIO_14_DIRECTION {inout} \

CONFIG.PSU_MIO_14_DRIVE_STRENGTH {4} \

CONFIG.PSU_MIO_14_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_14_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_14_SLEW {slow} \

CONFIG.PSU_MIO_15_DIRECTION {inout} \

CONFIG.PSU_MIO_15_DRIVE_STRENGTH {4} \

CONFIG.PSU_MIO_15_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_15_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_15_SLEW {slow} \

CONFIG.PSU_MIO_16_DIRECTION {inout} \

CONFIG.PSU_MIO_16_DRIVE_STRENGTH {4} \

CONFIG.PSU_MIO_16_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_16_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_16_SLEW {slow} \

CONFIG.PSU_MIO_17_DIRECTION {inout} \

CONFIG.PSU_MIO_17_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_17_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_17_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_17_SLEW {slow} \

CONFIG.PSU_MIO_18_DIRECTION {inout} \

CONFIG.PSU_MIO_18_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_18_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_18_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_18_SLEW {slow} \

CONFIG.PSU_MIO_19_DIRECTION {inout} \

CONFIG.PSU_MIO_19_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_19_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_19_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_19_SLEW {slow} \

CONFIG.PSU_MIO_1_DIRECTION {inout} \

CONFIG.PSU_MIO_1_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_1_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_1_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_1_SLEW {slow} \

CONFIG.PSU_MIO_20_DIRECTION {inout} \

CONFIG.PSU_MIO_20_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_20_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_20_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_20_SLEW {slow} \

CONFIG.PSU_MIO_21_DIRECTION {inout} \

CONFIG.PSU_MIO_21_DRIVE_STRENGTH {4} \

CONFIG.PSU_MIO_21_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_21_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_21_SLEW {slow} \

CONFIG.PSU_MIO_22_DIRECTION {out} \

CONFIG.PSU_MIO_22_DRIVE_STRENGTH {4} \

CONFIG.PSU_MIO_22_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_22_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_22_SLEW {slow} \

CONFIG.PSU_MIO_23_DIRECTION {inout} \

CONFIG.PSU_MIO_23_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_23_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_23_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_23_SLEW {slow} \

CONFIG.PSU_MIO_24_DIRECTION {in} \

CONFIG.PSU_MIO_24_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_24_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_24_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_24_SLEW {slow} \

CONFIG.PSU_MIO_25_DIRECTION {inout} \

CONFIG.PSU_MIO_25_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_25_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_25_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_25_SLEW {slow} \

CONFIG.PSU_MIO_26_DIRECTION {inout} \

CONFIG.PSU_MIO_26_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_26_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_26_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_26_SLEW {slow} \

CONFIG.PSU_MIO_27_DIRECTION {out} \

CONFIG.PSU_MIO_27_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_27_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_27_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_27_SLEW {slow} \

CONFIG.PSU_MIO_28_DIRECTION {in} \

CONFIG.PSU_MIO_28_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_28_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_28_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_28_SLEW {slow} \

CONFIG.PSU_MIO_29_DIRECTION {out} \

CONFIG.PSU_MIO_29_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_29_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_29_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_29_SLEW {slow} \

CONFIG.PSU_MIO_2_DIRECTION {in} \

CONFIG.PSU_MIO_2_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_2_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_2_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_2_SLEW {slow} \

CONFIG.PSU_MIO_30_DIRECTION {in} \

CONFIG.PSU_MIO_30_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_30_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_30_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_30_SLEW {slow} \

CONFIG.PSU_MIO_31_DIRECTION {inout} \

CONFIG.PSU_MIO_31_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_31_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_31_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_31_SLEW {slow} \

CONFIG.PSU_MIO_32_DIRECTION {out} \

CONFIG.PSU_MIO_32_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_32_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_32_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_32_SLEW {slow} \

CONFIG.PSU_MIO_33_DIRECTION {out} \

CONFIG.PSU_MIO_33_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_33_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_33_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_33_SLEW {slow} \

CONFIG.PSU_MIO_34_DIRECTION {inout} \

CONFIG.PSU_MIO_34_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_34_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_34_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_34_SLEW {slow} \

CONFIG.PSU_MIO_35_DIRECTION {inout} \

CONFIG.PSU_MIO_35_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_35_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_35_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_35_SLEW {slow} \

CONFIG.PSU_MIO_36_DIRECTION {inout} \

CONFIG.PSU_MIO_36_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_36_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_36_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_36_SLEW {slow} \

CONFIG.PSU_MIO_37_DIRECTION {inout} \

CONFIG.PSU_MIO_37_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_37_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_37_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_37_SLEW {slow} \

CONFIG.PSU_MIO_38_DIRECTION {inout} \

CONFIG.PSU_MIO_38_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_38_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_38_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_38_SLEW {slow} \

CONFIG.PSU_MIO_39_DIRECTION {inout} \

CONFIG.PSU_MIO_39_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_39_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_39_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_39_SLEW {slow} \

CONFIG.PSU_MIO_3_DIRECTION {out} \

CONFIG.PSU_MIO_3_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_3_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_3_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_3_SLEW {slow} \

CONFIG.PSU_MIO_40_DIRECTION {inout} \

CONFIG.PSU_MIO_40_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_40_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_40_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_40_SLEW {slow} \

CONFIG.PSU_MIO_41_DIRECTION {inout} \

CONFIG.PSU_MIO_41_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_41_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_41_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_41_SLEW {slow} \

CONFIG.PSU_MIO_42_DIRECTION {inout} \

CONFIG.PSU_MIO_42_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_42_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_42_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_42_SLEW {slow} \

CONFIG.PSU_MIO_43_DIRECTION {inout} \

CONFIG.PSU_MIO_43_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_43_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_43_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_43_SLEW {slow} \

CONFIG.PSU_MIO_44_DIRECTION {inout} \

CONFIG.PSU_MIO_44_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_44_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_44_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_44_SLEW {slow} \

CONFIG.PSU_MIO_45_DIRECTION {inout} \

CONFIG.PSU_MIO_45_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_45_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_45_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_45_SLEW {slow} \

CONFIG.PSU_MIO_46_DIRECTION {inout} \

CONFIG.PSU_MIO_46_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_46_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_46_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_46_SLEW {slow} \

CONFIG.PSU_MIO_47_DIRECTION {inout} \

CONFIG.PSU_MIO_47_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_47_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_47_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_47_SLEW {slow} \

CONFIG.PSU_MIO_48_DIRECTION {inout} \

CONFIG.PSU_MIO_48_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_48_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_48_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_48_SLEW {slow} \

CONFIG.PSU_MIO_49_DIRECTION {inout} \

CONFIG.PSU_MIO_49_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_49_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_49_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_49_SLEW {slow} \

CONFIG.PSU_MIO_4_DIRECTION {inout} \

CONFIG.PSU_MIO_4_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_4_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_4_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_4_SLEW {slow} \

CONFIG.PSU_MIO_50_DIRECTION {inout} \

CONFIG.PSU_MIO_50_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_50_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_50_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_50_SLEW {slow} \

CONFIG.PSU_MIO_51_DIRECTION {out} \

CONFIG.PSU_MIO_51_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_51_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_51_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_51_SLEW {slow} \

CONFIG.PSU_MIO_52_DIRECTION {in} \

CONFIG.PSU_MIO_52_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_52_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_52_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_52_SLEW {slow} \

CONFIG.PSU_MIO_53_DIRECTION {in} \

CONFIG.PSU_MIO_53_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_53_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_53_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_53_SLEW {slow} \

CONFIG.PSU_MIO_54_DIRECTION {inout} \

CONFIG.PSU_MIO_54_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_54_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_54_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_54_SLEW {slow} \

CONFIG.PSU_MIO_55_DIRECTION {in} \

CONFIG.PSU_MIO_55_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_55_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_55_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_55_SLEW {slow} \

CONFIG.PSU_MIO_56_DIRECTION {inout} \

CONFIG.PSU_MIO_56_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_56_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_56_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_56_SLEW {slow} \

CONFIG.PSU_MIO_57_DIRECTION {inout} \

CONFIG.PSU_MIO_57_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_57_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_57_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_57_SLEW {slow} \

CONFIG.PSU_MIO_58_DIRECTION {out} \

CONFIG.PSU_MIO_58_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_58_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_58_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_58_SLEW {slow} \

CONFIG.PSU_MIO_59_DIRECTION {inout} \

CONFIG.PSU_MIO_59_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_59_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_59_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_59_SLEW {slow} \

CONFIG.PSU_MIO_5_DIRECTION {inout} \

CONFIG.PSU_MIO_5_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_5_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_5_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_5_SLEW {slow} \

CONFIG.PSU_MIO_60_DIRECTION {inout} \

CONFIG.PSU_MIO_60_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_60_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_60_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_60_SLEW {slow} \

CONFIG.PSU_MIO_61_DIRECTION {inout} \

CONFIG.PSU_MIO_61_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_61_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_61_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_61_SLEW {slow} \

CONFIG.PSU_MIO_62_DIRECTION {inout} \

CONFIG.PSU_MIO_62_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_62_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_62_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_62_SLEW {slow} \

CONFIG.PSU_MIO_63_DIRECTION {inout} \

CONFIG.PSU_MIO_63_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_63_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_63_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_63_SLEW {slow} \

CONFIG.PSU_MIO_64_DIRECTION {in} \

CONFIG.PSU_MIO_64_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_64_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_64_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_64_SLEW {slow} \

CONFIG.PSU_MIO_65_DIRECTION {in} \

CONFIG.PSU_MIO_65_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_65_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_65_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_65_SLEW {slow} \

CONFIG.PSU_MIO_66_DIRECTION {inout} \

CONFIG.PSU_MIO_66_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_66_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_66_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_66_SLEW {slow} \

CONFIG.PSU_MIO_67_DIRECTION {in} \

CONFIG.PSU_MIO_67_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_67_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_67_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_67_SLEW {slow} \

CONFIG.PSU_MIO_68_DIRECTION {inout} \

CONFIG.PSU_MIO_68_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_68_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_68_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_68_SLEW {slow} \

CONFIG.PSU_MIO_69_DIRECTION {inout} \

CONFIG.PSU_MIO_69_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_69_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_69_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_69_SLEW {slow} \

CONFIG.PSU_MIO_6_DIRECTION {inout} \

CONFIG.PSU_MIO_6_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_6_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_6_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_6_SLEW {slow} \

CONFIG.PSU_MIO_70_DIRECTION {out} \

CONFIG.PSU_MIO_70_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_70_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_70_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_70_SLEW {slow} \

CONFIG.PSU_MIO_71_DIRECTION {inout} \

CONFIG.PSU_MIO_71_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_71_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_71_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_71_SLEW {slow} \

CONFIG.PSU_MIO_72_DIRECTION {inout} \

CONFIG.PSU_MIO_72_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_72_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_72_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_72_SLEW {slow} \

CONFIG.PSU_MIO_73_DIRECTION {inout} \

CONFIG.PSU_MIO_73_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_73_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_73_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_73_SLEW {slow} \

CONFIG.PSU_MIO_74_DIRECTION {inout} \

CONFIG.PSU_MIO_74_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_74_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_74_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_74_SLEW {slow} \

CONFIG.PSU_MIO_75_DIRECTION {inout} \

CONFIG.PSU_MIO_75_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_75_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_75_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_75_SLEW {slow} \

CONFIG.PSU_MIO_76_DIRECTION {inout} \

CONFIG.PSU_MIO_76_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_76_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_76_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_76_SLEW {slow} \

CONFIG.PSU_MIO_77_DIRECTION {inout} \

CONFIG.PSU_MIO_77_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_77_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_77_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_77_SLEW {slow} \

CONFIG.PSU_MIO_7_DIRECTION {inout} \

CONFIG.PSU_MIO_7_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_7_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_7_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_7_SLEW {slow} \

CONFIG.PSU_MIO_8_DIRECTION {inout} \

CONFIG.PSU_MIO_8_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_8_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_8_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_8_SLEW {slow} \

CONFIG.PSU_MIO_9_DIRECTION {inout} \

CONFIG.PSU_MIO_9_DRIVE_STRENGTH {12} \

CONFIG.PSU_MIO_9_INPUT_TYPE {schmitt} \

CONFIG.PSU_MIO_9_PULLUPDOWN {pullup} \

CONFIG.PSU_MIO_9_SLEW {slow} \

CONFIG.PSU_MIO_TREE_PERIPHERALS {GPIO0 MIO#GPIO0 MIO#UART 0#UART 0#I2C 1#I2C 1#SPI 1#GPIO0 MIO#GPIO0 MIO#SPI 1#SPI 1#SPI 1#GPIO0 MIO#SD 0#SD 0#SD 0#SD 0#GPIO0 MIO#GPIO0 MIO#GPIO0 MIO#GPIO0 MIO#SD 0#SD 0#GPIO0 MIO#SD 0#GPIO0 MIO#GPIO1 MIO#DPAUX#DPAUX#DPAUX#DPAUX#GPIO1 MIO#PMU GPO 0#PMU GPO 1#GPIO1 MIO#GPIO1 MIO#GPIO1 MIO#GPIO1 MIO#SPI 0#GPIO1 MIO#GPIO1 MIO#SPI 0#SPI 0#SPI 0#GPIO1 MIO#GPIO1 MIO#SD 1#SD 1#SD 1#SD 1#SD 1#SD 1#USB 0#USB 0#USB 0#USB 0#USB 0#USB 0#USB 0#USB 0#USB 0#USB 0#USB 0#USB 0#USB 1#USB 1#USB 1#USB 1#USB 1#USB 1#USB 1#USB 1#USB 1#USB 1#USB 1#USB 1#GPIO2 MIO#GPIO2 MIO} \

CONFIG.PSU_MIO_TREE_SIGNALS {gpio0[0]#gpio0[1]#rxd#txd#scl_out#sda_out#sclk_out#gpio0[7]#gpio0[8]#n_ss_out[0]#miso#mosi#gpio0[12]#sdio0_data_out[0]#sdio0_data_out[1]#sdio0_data_out[2]#sdio0_data_out[3]#gpio0[17]#gpio0[18]#gpio0[19]#gpio0[20]#sdio0_cmd_out#sdio0_clk_out#gpio0[23]#sdio0_cd_n#gpio0[25]#gpio1[26]#dp_aux_data_out#dp_hot_plug_detect#dp_aux_data_oe#dp_aux_data_in#gpio1[31]#gpo[0]#gpo[1]#gpio1[34]#gpio1[35]#gpio1[36]#gpio1[37]#sclk_out#gpio1[39]#gpio1[40]#n_ss_out[0]#miso#mosi#gpio1[44]#gpio1[45]#sdio1_data_out[0]#sdio1_data_out[1]#sdio1_data_out[2]#sdio1_data_out[3]#sdio1_cmd_out#sdio1_clk_out#ulpi_clk_in#ulpi_dir#ulpi_tx_data[2]#ulpi_nxt#ulpi_tx_data[0]#ulpi_tx_data[1]#ulpi_stp#ulpi_tx_data[3]#ulpi_tx_data[4]#ulpi_tx_data[5]#ulpi_tx_data[6]#ulpi_tx_data[7]#ulpi_clk_in#ulpi_dir#ulpi_tx_data[2]#ulpi_nxt#ulpi_tx_data[0]#ulpi_tx_data[1]#ulpi_stp#ulpi_tx_data[3]#ulpi_tx_data[4]#ulpi_tx_data[5]#ulpi_tx_data[6]#ulpi_tx_data[7]#gpio2[76]#gpio2[77]} \

CONFIG.PSU_PERIPHERAL_BOARD_PRESET {} \

CONFIG.PSU_SD0_INTERNAL_BUS_WIDTH {4} \

CONFIG.PSU_SD1_INTERNAL_BUS_WIDTH {4} \

CONFIG.PSU_SMC_CYCLE_T0 {NA} \

CONFIG.PSU_SMC_CYCLE_T1 {NA} \

CONFIG.PSU_SMC_CYCLE_T2 {NA} \

CONFIG.PSU_SMC_CYCLE_T3 {NA} \

CONFIG.PSU_SMC_CYCLE_T4 {NA} \

CONFIG.PSU_SMC_CYCLE_T5 {NA} \

CONFIG.PSU_SMC_CYCLE_T6 {NA} \

CONFIG.PSU_VALUE_SILVERSION {3} \

CONFIG.PSU__ACPU0__POWER__ON {1} \

CONFIG.PSU__ACPU1__POWER__ON {1} \

CONFIG.PSU__ACPU2__POWER__ON {1} \

CONFIG.PSU__ACPU3__POWER__ON {1} \

CONFIG.PSU__ACTUAL__IP {1} \

CONFIG.PSU__ACT_DDR_FREQ_MHZ {533.332825} \

CONFIG.PSU__AFI0_COHERENCY {0} \

CONFIG.PSU__AFI1_COHERENCY {0} \

CONFIG.PSU__AUX_REF_CLK__FREQMHZ {33.333} \

CONFIG.PSU__CAN0_LOOP_CAN1__ENABLE {0} \

CONFIG.PSU__CAN0__GRP_CLK__ENABLE {0} \

CONFIG.PSU__CAN0__PERIPHERAL__ENABLE {0} \

CONFIG.PSU__CAN1__GRP_CLK__ENABLE {0} \

CONFIG.PSU__CAN1__PERIPHERAL__ENABLE {0} \

CONFIG.PSU__CRF_APB__ACPU_CTRL__ACT_FREQMHZ {1199.998901} \

CONFIG.PSU__CRF_APB__ACPU_CTRL__DIVISOR0 {1} \

CONFIG.PSU__CRF_APB__ACPU_CTRL__FREQMHZ {1200} \

CONFIG.PSU__CRF_APB__ACPU_CTRL__SRCSEL {APLL} \

CONFIG.PSU__CRF_APB__ACPU__FRAC_ENABLED {0} \

CONFIG.PSU__CRF_APB__AFI0_REF_CTRL__ACT_FREQMHZ {667} \

CONFIG.PSU__CRF_APB__AFI0_REF_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__AFI0_REF_CTRL__FREQMHZ {667} \

CONFIG.PSU__CRF_APB__AFI0_REF_CTRL__SRCSEL {DPLL} \

CONFIG.PSU__CRF_APB__AFI0_REF__ENABLE {0} \

CONFIG.PSU__CRF_APB__AFI1_REF_CTRL__ACT_FREQMHZ {667} \

CONFIG.PSU__CRF_APB__AFI1_REF_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__AFI1_REF_CTRL__FREQMHZ {667} \

CONFIG.PSU__CRF_APB__AFI1_REF_CTRL__SRCSEL {DPLL} \

CONFIG.PSU__CRF_APB__AFI1_REF__ENABLE {0} \

CONFIG.PSU__CRF_APB__AFI2_REF_CTRL__ACT_FREQMHZ {667} \

CONFIG.PSU__CRF_APB__AFI2_REF_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__AFI2_REF_CTRL__FREQMHZ {667} \

CONFIG.PSU__CRF_APB__AFI2_REF_CTRL__SRCSEL {DPLL} \

CONFIG.PSU__CRF_APB__AFI2_REF__ENABLE {0} \

CONFIG.PSU__CRF_APB__AFI3_REF_CTRL__ACT_FREQMHZ {667} \

CONFIG.PSU__CRF_APB__AFI3_REF_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__AFI3_REF_CTRL__FREQMHZ {667} \

CONFIG.PSU__CRF_APB__AFI3_REF_CTRL__SRCSEL {DPLL} \

CONFIG.PSU__CRF_APB__AFI3_REF__ENABLE {0} \

CONFIG.PSU__CRF_APB__AFI4_REF_CTRL__ACT_FREQMHZ {667} \

CONFIG.PSU__CRF_APB__AFI4_REF_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__AFI4_REF_CTRL__FREQMHZ {667} \

CONFIG.PSU__CRF_APB__AFI4_REF_CTRL__SRCSEL {DPLL} \

CONFIG.PSU__CRF_APB__AFI4_REF__ENABLE {0} \

CONFIG.PSU__CRF_APB__AFI5_REF_CTRL__ACT_FREQMHZ {667} \

CONFIG.PSU__CRF_APB__AFI5_REF_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__AFI5_REF_CTRL__FREQMHZ {667} \

CONFIG.PSU__CRF_APB__AFI5_REF_CTRL__SRCSEL {DPLL} \

CONFIG.PSU__CRF_APB__AFI5_REF__ENABLE {0} \

CONFIG.PSU__CRF_APB__APLL_CTRL__DIV2 {1} \

CONFIG.PSU__CRF_APB__APLL_CTRL__FBDIV {72} \

CONFIG.PSU__CRF_APB__APLL_CTRL__FRACDATA {0} \

CONFIG.PSU__CRF_APB__APLL_CTRL__FRACFREQ {27.138} \

CONFIG.PSU__CRF_APB__APLL_CTRL__SRCSEL {PSS_REF_CLK} \

CONFIG.PSU__CRF_APB__APLL_FRAC_CFG__ENABLED {0} \

CONFIG.PSU__CRF_APB__APLL_TO_LPD_CTRL__DIVISOR0 {3} \

CONFIG.PSU__CRF_APB__APM_CTRL__ACT_FREQMHZ {1} \

CONFIG.PSU__CRF_APB__APM_CTRL__DIVISOR0 {1} \

CONFIG.PSU__CRF_APB__APM_CTRL__FREQMHZ {1} \

CONFIG.PSU__CRF_APB__DBG_FPD_CTRL__ACT_FREQMHZ {249.999756} \

CONFIG.PSU__CRF_APB__DBG_FPD_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__DBG_FPD_CTRL__FREQMHZ {250} \

CONFIG.PSU__CRF_APB__DBG_FPD_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRF_APB__DBG_TRACE_CTRL__ACT_FREQMHZ {250} \

CONFIG.PSU__CRF_APB__DBG_TRACE_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__DBG_TRACE_CTRL__FREQMHZ {250} \

CONFIG.PSU__CRF_APB__DBG_TRACE_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRF_APB__DBG_TSTMP_CTRL__ACT_FREQMHZ {249.999756} \

CONFIG.PSU__CRF_APB__DBG_TSTMP_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__DBG_TSTMP_CTRL__FREQMHZ {250} \

CONFIG.PSU__CRF_APB__DBG_TSTMP_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRF_APB__DDR_CTRL__ACT_FREQMHZ {266.666412} \

CONFIG.PSU__CRF_APB__DDR_CTRL__DIVISOR0 {4} \

CONFIG.PSU__CRF_APB__DDR_CTRL__FREQMHZ {533} \

CONFIG.PSU__CRF_APB__DDR_CTRL__SRCSEL {DPLL} \

CONFIG.PSU__CRF_APB__DPDMA_REF_CTRL__ACT_FREQMHZ {599.999451} \

CONFIG.PSU__CRF_APB__DPDMA_REF_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__DPDMA_REF_CTRL__FREQMHZ {600} \

CONFIG.PSU__CRF_APB__DPDMA_REF_CTRL__SRCSEL {APLL} \

CONFIG.PSU__CRF_APB__DPLL_CTRL__DIV2 {1} \

CONFIG.PSU__CRF_APB__DPLL_CTRL__FBDIV {64} \

CONFIG.PSU__CRF_APB__DPLL_CTRL__FRACDATA {0} \

CONFIG.PSU__CRF_APB__DPLL_CTRL__FRACFREQ {27.138} \

CONFIG.PSU__CRF_APB__DPLL_CTRL__SRCSEL {PSS_REF_CLK} \

CONFIG.PSU__CRF_APB__DPLL_FRAC_CFG__ENABLED {0} \

CONFIG.PSU__CRF_APB__DPLL_TO_LPD_CTRL__DIVISOR0 {3} \

CONFIG.PSU__CRF_APB__DP_AUDIO_REF_CTRL__ACT_FREQMHZ {24.576017} \

CONFIG.PSU__CRF_APB__DP_AUDIO_REF_CTRL__DIVISOR0 {16} \

CONFIG.PSU__CRF_APB__DP_AUDIO_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRF_APB__DP_AUDIO_REF_CTRL__FREQMHZ {25} \

CONFIG.PSU__CRF_APB__DP_AUDIO_REF_CTRL__SRCSEL {RPLL} \

CONFIG.PSU__CRF_APB__DP_AUDIO__FRAC_ENABLED {1} \

CONFIG.PSU__CRF_APB__DP_STC_REF_CTRL__ACT_FREQMHZ {26.214418} \

CONFIG.PSU__CRF_APB__DP_STC_REF_CTRL__DIVISOR0 {15} \

CONFIG.PSU__CRF_APB__DP_STC_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRF_APB__DP_STC_REF_CTRL__FREQMHZ {27} \

CONFIG.PSU__CRF_APB__DP_STC_REF_CTRL__SRCSEL {RPLL} \

CONFIG.PSU__CRF_APB__DP_VIDEO_REF_CTRL__ACT_FREQMHZ {297.029297} \

CONFIG.PSU__CRF_APB__DP_VIDEO_REF_CTRL__DIVISOR0 {4} \

CONFIG.PSU__CRF_APB__DP_VIDEO_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRF_APB__DP_VIDEO_REF_CTRL__FREQMHZ {300} \

CONFIG.PSU__CRF_APB__DP_VIDEO_REF_CTRL__SRCSEL {VPLL} \

CONFIG.PSU__CRF_APB__DP_VIDEO__FRAC_ENABLED {1} \

CONFIG.PSU__CRF_APB__GDMA_REF_CTRL__ACT_FREQMHZ {599.999451} \

CONFIG.PSU__CRF_APB__GDMA_REF_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__GDMA_REF_CTRL__FREQMHZ {600} \

CONFIG.PSU__CRF_APB__GDMA_REF_CTRL__SRCSEL {APLL} \

CONFIG.PSU__CRF_APB__GPU_REF_CTRL__ACT_FREQMHZ {499.999512} \

CONFIG.PSU__CRF_APB__GPU_REF_CTRL__DIVISOR0 {1} \

CONFIG.PSU__CRF_APB__GPU_REF_CTRL__FREQMHZ {600} \

CONFIG.PSU__CRF_APB__GPU_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRF_APB__GTGREF0_REF_CTRL__ACT_FREQMHZ {-1} \

CONFIG.PSU__CRF_APB__GTGREF0_REF_CTRL__DIVISOR0 {-1} \

CONFIG.PSU__CRF_APB__GTGREF0_REF_CTRL__FREQMHZ {-1} \

CONFIG.PSU__CRF_APB__GTGREF0_REF_CTRL__SRCSEL {NA} \

CONFIG.PSU__CRF_APB__GTGREF0__ENABLE {NA} \

CONFIG.PSU__CRF_APB__PCIE_REF_CTRL__ACT_FREQMHZ {250} \

CONFIG.PSU__CRF_APB__PCIE_REF_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__PCIE_REF_CTRL__FREQMHZ {250} \

CONFIG.PSU__CRF_APB__PCIE_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRF_APB__SATA_REF_CTRL__ACT_FREQMHZ {250} \

CONFIG.PSU__CRF_APB__SATA_REF_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__SATA_REF_CTRL__FREQMHZ {250} \

CONFIG.PSU__CRF_APB__SATA_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRF_APB__TOPSW_LSBUS_CTRL__ACT_FREQMHZ {99.999901} \

CONFIG.PSU__CRF_APB__TOPSW_LSBUS_CTRL__DIVISOR0 {5} \

CONFIG.PSU__CRF_APB__TOPSW_LSBUS_CTRL__FREQMHZ {100} \

CONFIG.PSU__CRF_APB__TOPSW_LSBUS_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRF_APB__TOPSW_MAIN_CTRL__ACT_FREQMHZ {533.332825} \

CONFIG.PSU__CRF_APB__TOPSW_MAIN_CTRL__DIVISOR0 {2} \

CONFIG.PSU__CRF_APB__TOPSW_MAIN_CTRL__FREQMHZ {533.333} \

CONFIG.PSU__CRF_APB__TOPSW_MAIN_CTRL__SRCSEL {DPLL} \

CONFIG.PSU__CRF_APB__VPLL_CTRL__DIV2 {1} \

CONFIG.PSU__CRF_APB__VPLL_CTRL__FBDIV {71} \

CONFIG.PSU__CRF_APB__VPLL_CTRL__FRACDATA {0.2871} \

CONFIG.PSU__CRF_APB__VPLL_CTRL__FRACFREQ {300} \

CONFIG.PSU__CRF_APB__VPLL_CTRL__SRCSEL {PSS_REF_CLK} \

CONFIG.PSU__CRF_APB__VPLL_FRAC_CFG__ENABLED {1} \

CONFIG.PSU__CRF_APB__VPLL_TO_LPD_CTRL__DIVISOR0 {3} \

CONFIG.PSU__CRL_APB__ADMA_REF_CTRL__ACT_FREQMHZ {499.999512} \

CONFIG.PSU__CRL_APB__ADMA_REF_CTRL__DIVISOR0 {3} \

CONFIG.PSU__CRL_APB__ADMA_REF_CTRL__FREQMHZ {500} \

CONFIG.PSU__CRL_APB__ADMA_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__AFI6_REF_CTRL__ACT_FREQMHZ {500} \

CONFIG.PSU__CRL_APB__AFI6_REF_CTRL__DIVISOR0 {3} \

CONFIG.PSU__CRL_APB__AFI6_REF_CTRL__FREQMHZ {500} \

CONFIG.PSU__CRL_APB__AFI6_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__AFI6__ENABLE {0} \

CONFIG.PSU__CRL_APB__AMS_REF_CTRL__ACT_FREQMHZ {51.724087} \

CONFIG.PSU__CRL_APB__AMS_REF_CTRL__DIVISOR0 {29} \

CONFIG.PSU__CRL_APB__AMS_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__AMS_REF_CTRL__FREQMHZ {50} \

CONFIG.PSU__CRL_APB__AMS_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__CAN0_REF_CTRL__ACT_FREQMHZ {100} \

CONFIG.PSU__CRL_APB__CAN0_REF_CTRL__DIVISOR0 {15} \

CONFIG.PSU__CRL_APB__CAN0_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__CAN0_REF_CTRL__FREQMHZ {100} \

CONFIG.PSU__CRL_APB__CAN0_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__CAN1_REF_CTRL__ACT_FREQMHZ {100} \

CONFIG.PSU__CRL_APB__CAN1_REF_CTRL__DIVISOR0 {15} \

CONFIG.PSU__CRL_APB__CAN1_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__CAN1_REF_CTRL__FREQMHZ {100} \

CONFIG.PSU__CRL_APB__CAN1_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__CPU_R5_CTRL__ACT_FREQMHZ {499.999512} \

CONFIG.PSU__CRL_APB__CPU_R5_CTRL__DIVISOR0 {3} \

CONFIG.PSU__CRL_APB__CPU_R5_CTRL__FREQMHZ {500} \

CONFIG.PSU__CRL_APB__CPU_R5_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__CSU_PLL_CTRL__ACT_FREQMHZ {500} \

CONFIG.PSU__CRL_APB__CSU_PLL_CTRL__DIVISOR0 {4} \

CONFIG.PSU__CRL_APB__CSU_PLL_CTRL__FREQMHZ {400} \

CONFIG.PSU__CRL_APB__CSU_PLL_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__DBG_LPD_CTRL__ACT_FREQMHZ {249.999756} \

CONFIG.PSU__CRL_APB__DBG_LPD_CTRL__DIVISOR0 {6} \

CONFIG.PSU__CRL_APB__DBG_LPD_CTRL__FREQMHZ {250} \

CONFIG.PSU__CRL_APB__DBG_LPD_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__DEBUG_R5_ATCLK_CTRL__ACT_FREQMHZ {1000} \

CONFIG.PSU__CRL_APB__DEBUG_R5_ATCLK_CTRL__DIVISOR0 {6} \

CONFIG.PSU__CRL_APB__DEBUG_R5_ATCLK_CTRL__FREQMHZ {1000} \

CONFIG.PSU__CRL_APB__DEBUG_R5_ATCLK_CTRL__SRCSEL {RPLL} \

CONFIG.PSU__CRL_APB__DLL_REF_CTRL__ACT_FREQMHZ {1499.998535} \

CONFIG.PSU__CRL_APB__DLL_REF_CTRL__FREQMHZ {1500} \

CONFIG.PSU__CRL_APB__DLL_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__GEM0_REF_CTRL__ACT_FREQMHZ {125} \

CONFIG.PSU__CRL_APB__GEM0_REF_CTRL__DIVISOR0 {12} \

CONFIG.PSU__CRL_APB__GEM0_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__GEM0_REF_CTRL__FREQMHZ {125} \

CONFIG.PSU__CRL_APB__GEM0_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__GEM1_REF_CTRL__ACT_FREQMHZ {125} \

CONFIG.PSU__CRL_APB__GEM1_REF_CTRL__DIVISOR0 {12} \

CONFIG.PSU__CRL_APB__GEM1_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__GEM1_REF_CTRL__FREQMHZ {125} \

CONFIG.PSU__CRL_APB__GEM1_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__GEM2_REF_CTRL__ACT_FREQMHZ {125} \

CONFIG.PSU__CRL_APB__GEM2_REF_CTRL__DIVISOR0 {12} \

CONFIG.PSU__CRL_APB__GEM2_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__GEM2_REF_CTRL__FREQMHZ {125} \

CONFIG.PSU__CRL_APB__GEM2_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__GEM3_REF_CTRL__ACT_FREQMHZ {125} \

CONFIG.PSU__CRL_APB__GEM3_REF_CTRL__DIVISOR0 {12} \

CONFIG.PSU__CRL_APB__GEM3_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__GEM3_REF_CTRL__FREQMHZ {125} \

CONFIG.PSU__CRL_APB__GEM3_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__GEM_TSU_REF_CTRL__ACT_FREQMHZ {250} \

CONFIG.PSU__CRL_APB__GEM_TSU_REF_CTRL__DIVISOR0 {6} \

CONFIG.PSU__CRL_APB__GEM_TSU_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__GEM_TSU_REF_CTRL__FREQMHZ {250} \

CONFIG.PSU__CRL_APB__GEM_TSU_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__I2C0_REF_CTRL__ACT_FREQMHZ {100} \

CONFIG.PSU__CRL_APB__I2C0_REF_CTRL__DIVISOR0 {15} \

CONFIG.PSU__CRL_APB__I2C0_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__I2C0_REF_CTRL__FREQMHZ {100} \

CONFIG.PSU__CRL_APB__I2C0_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__I2C1_REF_CTRL__ACT_FREQMHZ {99.999901} \

CONFIG.PSU__CRL_APB__I2C1_REF_CTRL__DIVISOR0 {15} \

CONFIG.PSU__CRL_APB__I2C1_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__I2C1_REF_CTRL__FREQMHZ {100} \

CONFIG.PSU__CRL_APB__I2C1_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__IOPLL_CTRL__DIV2 {0} \

CONFIG.PSU__CRL_APB__IOPLL_CTRL__FBDIV {45} \

CONFIG.PSU__CRL_APB__IOPLL_CTRL__FRACDATA {0} \

CONFIG.PSU__CRL_APB__IOPLL_CTRL__FRACFREQ {27.138} \

CONFIG.PSU__CRL_APB__IOPLL_CTRL__SRCSEL {PSS_REF_CLK} \

CONFIG.PSU__CRL_APB__IOPLL_FRAC_CFG__ENABLED {0} \

CONFIG.PSU__CRL_APB__IOPLL_TO_FPD_CTRL__DIVISOR0 {3} \

CONFIG.PSU__CRL_APB__IOU_SWITCH_CTRL__ACT_FREQMHZ {249.999756} \

CONFIG.PSU__CRL_APB__IOU_SWITCH_CTRL__DIVISOR0 {6} \

CONFIG.PSU__CRL_APB__IOU_SWITCH_CTRL__FREQMHZ {267} \

CONFIG.PSU__CRL_APB__IOU_SWITCH_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__LPD_LSBUS_CTRL__ACT_FREQMHZ {99.999901} \

CONFIG.PSU__CRL_APB__LPD_LSBUS_CTRL__DIVISOR0 {15} \

CONFIG.PSU__CRL_APB__LPD_LSBUS_CTRL__FREQMHZ {100} \

CONFIG.PSU__CRL_APB__LPD_LSBUS_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__LPD_SWITCH_CTRL__ACT_FREQMHZ {499.999512} \

CONFIG.PSU__CRL_APB__LPD_SWITCH_CTRL__DIVISOR0 {3} \

CONFIG.PSU__CRL_APB__LPD_SWITCH_CTRL__FREQMHZ {500} \

CONFIG.PSU__CRL_APB__LPD_SWITCH_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__NAND_REF_CTRL__ACT_FREQMHZ {100} \

CONFIG.PSU__CRL_APB__NAND_REF_CTRL__DIVISOR0 {15} \

CONFIG.PSU__CRL_APB__NAND_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__NAND_REF_CTRL__FREQMHZ {100} \

CONFIG.PSU__CRL_APB__NAND_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__OCM_MAIN_CTRL__ACT_FREQMHZ {500} \

CONFIG.PSU__CRL_APB__OCM_MAIN_CTRL__DIVISOR0 {3} \

CONFIG.PSU__CRL_APB__OCM_MAIN_CTRL__FREQMHZ {500} \

CONFIG.PSU__CRL_APB__OCM_MAIN_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__PCAP_CTRL__ACT_FREQMHZ {187.499817} \

CONFIG.PSU__CRL_APB__PCAP_CTRL__DIVISOR0 {8} \

CONFIG.PSU__CRL_APB__PCAP_CTRL__FREQMHZ {200} \

CONFIG.PSU__CRL_APB__PCAP_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__PL0_REF_CTRL__ACT_FREQMHZ {99.999901} \

CONFIG.PSU__CRL_APB__PL0_REF_CTRL__DIVISOR0 {15} \

CONFIG.PSU__CRL_APB__PL0_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__PL0_REF_CTRL__FREQMHZ {100} \

CONFIG.PSU__CRL_APB__PL0_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__PL1_REF_CTRL__ACT_FREQMHZ {24.999975} \

CONFIG.PSU__CRL_APB__PL1_REF_CTRL__DIVISOR0 {15} \

CONFIG.PSU__CRL_APB__PL1_REF_CTRL__DIVISOR1 {4} \

CONFIG.PSU__CRL_APB__PL1_REF_CTRL__FREQMHZ {100} \

CONFIG.PSU__CRL_APB__PL1_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__PL2_REF_CTRL__ACT_FREQMHZ {299.999695} \

CONFIG.PSU__CRL_APB__PL2_REF_CTRL__DIVISOR0 {5} \

CONFIG.PSU__CRL_APB__PL2_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__PL2_REF_CTRL__FREQMHZ {100} \

CONFIG.PSU__CRL_APB__PL2_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__PL3_REF_CTRL__ACT_FREQMHZ {374.999634} \

CONFIG.PSU__CRL_APB__PL3_REF_CTRL__DIVISOR0 {4} \

CONFIG.PSU__CRL_APB__PL3_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__PL3_REF_CTRL__FREQMHZ {100} \

CONFIG.PSU__CRL_APB__PL3_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__QSPI_REF_CTRL__ACT_FREQMHZ {300} \

CONFIG.PSU__CRL_APB__QSPI_REF_CTRL__DIVISOR0 {12} \

CONFIG.PSU__CRL_APB__QSPI_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__QSPI_REF_CTRL__FREQMHZ {300} \

CONFIG.PSU__CRL_APB__QSPI_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__RPLL_CTRL__DIV2 {1} \

CONFIG.PSU__CRL_APB__RPLL_CTRL__FBDIV {70} \

CONFIG.PSU__CRL_APB__RPLL_CTRL__FRACDATA {0.779} \

CONFIG.PSU__CRL_APB__RPLL_CTRL__FRACFREQ {25} \

CONFIG.PSU__CRL_APB__RPLL_CTRL__SRCSEL {PSS_REF_CLK} \

CONFIG.PSU__CRL_APB__RPLL_FRAC_CFG__ENABLED {1} \

CONFIG.PSU__CRL_APB__RPLL_TO_FPD_CTRL__DIVISOR0 {3} \

CONFIG.PSU__CRL_APB__SDIO0_REF_CTRL__ACT_FREQMHZ {187.499817} \

CONFIG.PSU__CRL_APB__SDIO0_REF_CTRL__DIVISOR0 {8} \

CONFIG.PSU__CRL_APB__SDIO0_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__SDIO0_REF_CTRL__FREQMHZ {200} \

CONFIG.PSU__CRL_APB__SDIO0_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__SDIO1_REF_CTRL__ACT_FREQMHZ {187.499817} \

CONFIG.PSU__CRL_APB__SDIO1_REF_CTRL__DIVISOR0 {8} \

CONFIG.PSU__CRL_APB__SDIO1_REF_CTRL__DIVISOR1 {1} \

CONFIG.PSU__CRL_APB__SDIO1_REF_CTRL__FREQMHZ {200} \

CONFIG.PSU__CRL_APB__SDIO1_REF_CTRL__SRCSEL {IOPLL} \

CONFIG.PSU__CRL_APB__SPI0_REF_CTRL__ACT_FREQMHZ {187.499817} \

...

This file has been truncated, please download it to see its full contents.

apb3_bram_cntrl.v

VerilogCustom APB3 based memory controller to interface TX and RX RAMs that store int16 values

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

//

// Copyright 2019 Xilinx

//

// Licensed under the Apache License, Version 2.0 (the "License");

// you may not use this file except in compliance with the License.

// You may obtain a copy of the License at

//

// http://www.apache.org/licenses/LICENSE-2.0

//

// Unless required by applicable law or agreed to in writing, software

// distributed under the License is distributed on an "AS IS" BASIS,

// WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

// See the License for the specific language governing permissions and

// limitations under the License.

//

//////////////////////////////////////////////////////////////////////////////////

// Company: Xilinx

// Engineer: Rajeev Patwari

//

// Create Date: 05/23/2018 07:05:44 PM

// Design Name:

// Module Name: apb3_bram_cntrr

// Project Name: ZZSoC Proj 2 Nbody sim

// Target Devices: XCZU3EG

// Tool Versions: 2018.3

// Description:

// Custom APB3 based memory controller to interface TX and RX RAMs that

// store int16 values

//

// Dependencies:

//

// Revision:

// Revision 0.02 - Edited filename, changed addr with to 15 bits and added comments

// Additional Comments:

// 1. All code was designed and developed by me.

// 2. This engine receives commands from APB3 bus (through AXI to APB bridge)

// and decides where the WRITES/READS should be diverted to.

// 3. In sort, this acts like a mini memory controller

//////////////////////////////////////////////////////////////////////////////////

`define RAM_DEPTH 512

module apb3_bram_cntrl(

clk,

rst_in,

APB_M_paddr, // rx

APB_M_penable,

APB_M_psel,

APB_M_pwdata,

APB_M_pwrite,

APB_M_pready,

APB_M_prdata,

APB_M_pslverr,

APB_M2_paddr, // tx

APB_M2_penable,

APB_M2_psel,

APB_M2_pwdata,

APB_M2_pwrite,

APB_M2_pready,

APB_M2_prdata,

APB_M2_pslverr,

// rx ram - write to this ram through sw

// the following signals are generated from apb3 bram controller to write to rxram

addra_rxram0,

dina_rxram0,

wea_rxram0,

ena_rxram0,

douta_rxram0,

addra_rxram1,

dina_rxram1,

wea_rxram1,

ena_rxram1,

douta_rxram1,

// tx bram - read from this ram through sw

// the following signals are generated from apb3 bram controller to read from txram

addrb_txram0,

enb_txram0,

doutb_txram0,

addrb_txram1,

enb_txram1,

doutb_txram1

);

input clk;

input rst_in;

input wire [31:0] APB_M_paddr;

input wire APB_M_penable;

input wire [0:0] APB_M_psel;

input wire [31:0] APB_M_pwdata;

input wire APB_M_pwrite;

output wire [0:0] APB_M_pready;

output wire [31:0] APB_M_prdata;

output wire APB_M_pslverr;

input wire [31:0] APB_M2_paddr;

input wire APB_M2_penable;

input wire [0:0] APB_M2_psel;

input wire [31:0] APB_M2_pwdata;

input wire APB_M2_pwrite;

output wire [0:0] APB_M2_pready;

output wire [31:0] APB_M2_prdata;

output wire APB_M2_pslverr;

output wire [15:0] addra_rxram0;

output wire [31:0] dina_rxram0;

output wire wea_rxram0;

output wire ena_rxram0;

input wire [31:0] douta_rxram0;

output wire [15:0] addra_rxram1;

output wire [31:0] dina_rxram1;

output wire wea_rxram1;

output wire ena_rxram1;

input wire [31:0] douta_rxram1;

output wire [15:0] addrb_txram0;

output wire enb_txram0;

input wire [31:0] doutb_txram0;

output wire [15:0] addrb_txram1;

output wire enb_txram1;

input wire [31:0] doutb_txram1;

wire [15:0] rxaddr, txaddr;

wire [15:0] rxram_row_num, txram_row_num;

wire is_rxram1, is_txram1;

wire rxram_wr_en, txram_wr_en;

// local reset synchronizer

wire rst;

reset_pipe rst_pipe_apb3_bram_cntrl (.clk(clk), .rst_in(rst_in), .rst_out(rst));

//assign rst = rst_in;

//---------

// APB_M_addr is 16b address

// 0x0, 0x4, 0x8..

// apb - m - rxram0 - 0x0000 to 0x7FFF

// apb - m - rxram1 - 0x8000 to 0xFFFF

// apb - m2 - txram - 0x0000 to 0x7FFF

// rxram and txram addresses are just row nums (APB_M_addr>>2)

// rx brams : control - rxram0 has x,y & rxram1 has z,mass

assign rxaddr = APB_M_paddr[15:0]>>2;

assign rxram_row_num = {1'b0,rxaddr[14:0]};

assign is_rxram1 = APB_M_paddr[15];

assign APB_M_pready = 1'b1;

assign rxram_wr_en = APB_M_penable && APB_M_psel && APB_M_pwrite;

assign addra_rxram0 = rxram_row_num;

assign dina_rxram0 = (rxram_wr_en && ~is_rxram1) ? APB_M_pwdata : 32'd0;

assign wea_rxram0 = (rxram_wr_en && ~is_rxram1) ? 1'b1 : 1'd0;

assign ena_rxram0 = (~is_rxram1) ? 1'b1 : 1'd0;

assign addra_rxram1 = rxram_row_num;

assign dina_rxram1 = (rxram_wr_en && is_rxram1) ? APB_M_pwdata : 32'd0;

assign wea_rxram1 = (rxram_wr_en && is_rxram1) ? 1'b1 : 1'd0;

assign ena_rxram1 = (is_rxram1) ? 1'b1 : 1'd0;

assign APB_M_prdata = (is_rxram1) ? douta_rxram1 : douta_rxram0;

assign APB_M_pslverr = 1'b0;

// tx brams : control -

assign txaddr = APB_M2_paddr[15:0]>>2;

assign txram_row_num = {1'b0,txaddr[14:0]};

assign is_txram1 = APB_M2_paddr[15];

assign APB_M2_pready = 1'b1;

assign addrb_txram0 = txram_row_num;

assign addrb_txram1 = txram_row_num;

assign enb_txram0 = 1'b1;

assign enb_txram1 = 1'b1;

assign txram_wr_en = 1'b0;

assign APB_M2_pslverr = 1'b0;

assign APB_M2_prdata = (is_txram1) ? doutb_txram1 : doutb_txram0;

endmodule

apb3_regbank.v

VerilogCustom APB based control and status register space.

User can trigger accelerator and collect status signals from PL

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

//

// Copyright 2019 Xilinx

//

// Licensed under the Apache License, Version 2.0 (the "License");

// you may not use this file except in compliance with the License.

// You may obtain a copy of the License at

//

// http://www.apache.org/licenses/LICENSE-2.0

//

// Unless required by applicable law or agreed to in writing, software

// distributed under the License is distributed on an "AS IS" BASIS,

// WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

// See the License for the specific language governing permissions and

// limitations under the License.

//

//////////////////////////////////////////////////////////////////////////////////

// Company: Xilinx

// Engineer: Rajeev Patwari

//

// Create Date: 04/18/2018 08:30:50 PM

// Design Name:

// Module Name: apb3_regbank

// Project Name: ZZSoC Proj 2 Nbody sim

// Target Devices: XCZU3EG

// Tool Versions: 2018.3

// Description:

// Custome APB based control and status register space.

// User can trigger accelerator and collect status signals from PL

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

// All code designed, developed by me.

//////////////////////////////////////////////////////////////////////////////////

module apb3_regbank(

clk,

rst_in,

APB_M_paddr,

APB_M_penable,

APB_M_psel,

APB_M_pwdata,

APB_M_pwrite,

APB_M_pready,

APB_M_prdata,

APB_M_pslverr,

reg0,

reg1,

reg2,

reg3,

outreg0,

outreg1,

outreg2,

outreg3,

outreg4,

outreg5,

outreg6,

outreg7

);

input clk;

input rst_in;

input wire [31:0] APB_M_paddr;

input wire APB_M_penable;

input wire [0:0] APB_M_psel;

input wire [31:0] APB_M_pwdata;

input wire APB_M_pwrite;

output wire [0:0] APB_M_pready;

output reg [31:0] APB_M_prdata;

output wire APB_M_pslverr;

output reg [31:0] reg0;

output reg [31:0] reg1;

output reg [31:0] reg2;

output reg [31:0] reg3;

input wire [31:0] outreg0;

input wire [31:0] outreg1;

input wire [31:0] outreg2;

input wire [31:0] outreg3;

input wire [31:0] outreg4;

input wire [31:0] outreg5;