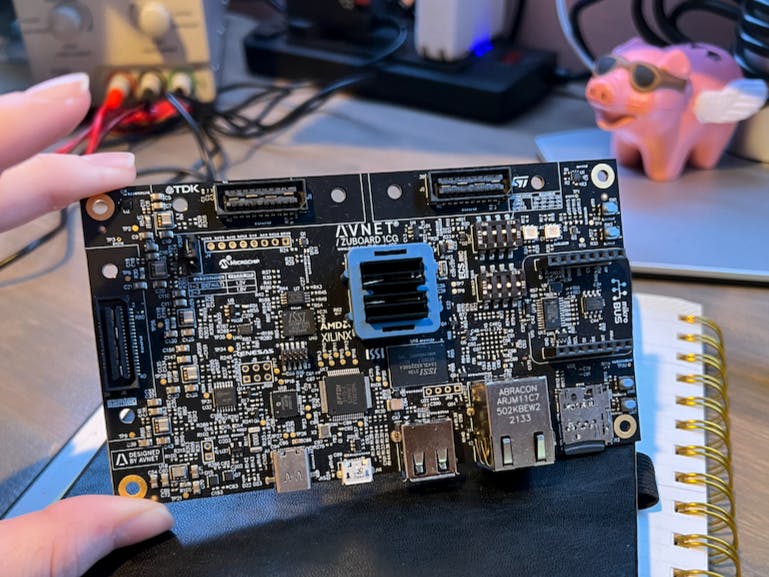

The ZUBoard is a new Zynq UltraScale+ MPSoC FPGA development board from Avnet. It is equipped with peripherals inlcuding 3 SYZYGY ports, Ethernet, a MikroE Click Expansion connector, and a USB TypeA port.

Users can get up and running in a straightforward manner thanks to Avnet's repositories of build scripts for Vivado and PetaLinux projects. This project demonstrates how to build the base Vivado and PetaLinux project using those build script from Avnet, as well as how to create a Vitis workspace for software application development.

Note: this project uses Vivado/Vitis/PetaLinux version 2022.1, but should work for versions 2020.1 and later.

Vivado ProjectCreate a directory to clone Avnet's board definition files (BDF) and HDL repositories into:

~$ mkdir -p avnet

~$ cd ./avnet/

~/avnet$ git clone https://github.com/avnet/bdf.git

~/avnet$ git clone https://github.com/avnet/hdl.gitAfter cloning the BDF and HDL repos change directories into the HDL directory to checkout the target Vivado version being used (which is 2022.1 for me at the moment):

~/avnet$ cd ./hdl/

~/avnet/hdl$ git checkout 2022.1After checking out the target version, source the Vivado tools to the environment and change directories into the scripts directory. Then use Vivado in batch mode to build the Vivado project for the target Avnet FPGA board using its TCL script. Most of the boards such as the ZUBoard have a couple different project options to select to build. For now, I went with the base project that provides the basic connections to the available peripherals on the ZUBoard:

~/avnet/hdl$ source /tools/Xilinx/Vivado/2022.1/settings64.sh

~/avnet/hdl$ cd ./scripts

~/avnet/hdl/scripts$ vivado -mode batch -source ./make_zub1cg_sbc_base.tclWait for the script to run and release the command line back, the time of which will vary depending on the complexity of the Vivado project being built (since the TCL scripts will create the Vivado project then run synthesis, implementation, and generate a bitstream).

If desired, launch the Vivado GUI to analyze the project and add any custom design.

~/avnet/hdl/scripts$ vivado &The project will be located in ./hdl/projects/<Avnet Board project name>/:

In the case of the base ZUBoard Vivado project, the option to run Block Automation can be ignored.

Avnet also provides a PetaLinux repository with script to build the base PetaLinux project for any of their boards as well as their respective BSPs (board support packages).

Clone the PetaLinux repository, I chose to keep it together in the same location where I cloned the BDF and HDL repositories:

~/avnet$ git clone https://github.com/avnet/petalinux.gitAgain, checkout the target version of PetaLinux being used (this should also match the target Vivado version used in the previous steps - 2022.1 again in my case):

~/avnet$ cd ./petalinux/

~/avnet/petalinux$ git checkout 2022.1Change directories in the the scripts directory and make sure both the PetaLinux and Vivado tools are sourced in the environment:

~/avnet/petalinux/scripts$ source /tools/Xilinx/Vivado/2022.1/settings64.sh

~/avnet/petalinux/scripts$ source /tools/Xilinx/PetaLinux/2022.1/settings.shThen run the build script for the desired Avnet FPGA board's PetaLinux project. Similar to the HDL projects, boards such as the ZUBoard have a couple different project options to select to build. Again, I'm opting to build the base PetaLinux project for the ZUBoard:

~/avnet/petalinux/scripts$ ./make_zub1cg_sbc_base.shThe PetaLinux project as well as its respective BSP are created in ./petalinux/projects:

With a base hardware design and embedded Linux image created for the ZUBoard, test out the hardware.

The SD card image created in the PetaLinux project is titled rootfs.wic located in ./petalinux/projects/images/linux. Flash an SD card with a program such as balenaEtcher and insert in the ZUBoard.

Set the boot mode switch (SW2) to SD (SW2-1: off SW2-1: on SW2-1: off SW2-1: on).

Plug in a USB C power supply capable of a DC output of 15V/3A and a micro USB cable for the serial output from the ZUBoard.

Finally, press SW7 to boot up the board.

Use any serial terminal application of choice (ie Putty, TeraTerm, etc.) at a baud rate of 115200 to see the UART output from the Linux image.

The default login username is root with no password.

Software Development in VitisIf desired, it is very straightforward to create a Vitis workspace from the Vivado project generated by the HDL repository in the first step. Users can develop both bare-metal (no-OS) and Linux applications and launch debug runs in the typical Eclipse workflow (both Vitis and its predecessor XSDK is Eclipse based).

Either source the Vitis tools to the environment in a terminal window and launch from the command line, or open the Vivado project created in step one and select Tools > Launch Vitis IDE

The directory to create the Vitis workspace can be any desired location in a directory owned by the current user. I personally prefer to create a directory in the top level of the corresponding Vivado project titled vitis_workspace to keep everything organized.

After launching into a blank workspace, the first step is to create the hardware platform project.

Select exported XSA file from the Vivado project (done automatically by the TCL scripts if built from the command line, but would need to be re-exported manually if any changes are made to the design and a new bitstream generated).

Select the desired operating system to build applications for, the target processor in the FPGA device, and whether or not to automatically generate the boot components for the processor.

After the platform project generates in the workspace, run a build (ctrl+B).

Next create the application project. Select the platform project just created to build it on then give the application the desired name on the next page.

Since I selected the bare-metal (standalone) as the OS for the platform project, that is the only option for the domain to create the application in.

Finally on the last page, there is a selection of application templates available for users. For demonstration purposes, I just went with the Hello World application template. I do use it as a convenient starting point for most of my bare-metal applications.

At this point, the typical Eclipse IDE flow for debugging, etc.

This same workflow can be followed for developing Linux C/C++ applications in Vitis (to run on the embedded Linux image created using PetaLinux).

Comments