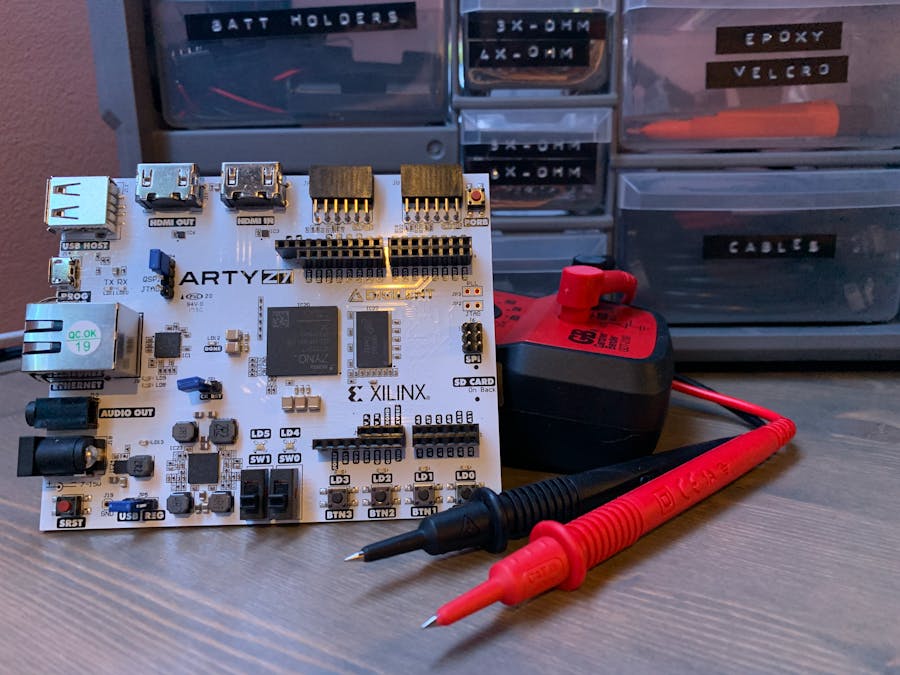

In this project, I will walk through the steps of setting up a basic hardware design in Vivado for the Arty Z7 FPGA development board from Digilent in Vivado version 2020.2. This hardware design is the starting point for my PetaLinux 2020.2 tutorial found here.

Install Board Definition FilesSince the FPGA on the Arty Z7 has a certain set of hardware that it is always connected to on the development board, Digilent (as well as many other companies that design/sell Xilinx-based FPGA development boards) provides board preset files for those static configurations that users can install in their Vivado installation. This allows users to not have to spend time configuring that part of the hardware design, and jump straight to the custom part of their design.

Download the board preset files for all Digilent FPGA development boards here. Unzip the folder and copy the contents of the /new/board_files folder into /<Vivado installation path>/data/boards/board_files. If Vivado was running when the files were copied over, it will need to be restarted before it will see the newly added board preset files.

Launch Vivado and select the option to create a new project. Give it the desired name and specify the desired file path in the first few windows that pop up. One of the windows will ask what project type is being created. This is a basic RTL Project being created that is not an extensible Vitis platform, meaning that it is not a project targeting accelerated applications and the specialized components such as the specific kernel they require. Therefore leave the Project is an extensible Vitis platform box unchecked. Unless you have RTL files (Verilog or VHDL files) to ready to import into the project already, check the box Do not specify sources at the time.

In order to make the board preset files for the Arty Z7 board accessible in this project that were installed in Vivado in the previous step, switch to the Boards tab in the Default Part window and search the key term Arty. I'm using the Arty Z7-20 version of the Arty board, but be sure to select the respective Arty model you are using.

Once the new project has been generated, the first step is to create a new block design. Select the Create Block Design option from the Flow Navigator window on the left of the Vivado window.

After the blank block design generates, click the + symbol in the middle and type zynq into the search bar of the window that appears. Double-click on the ZYNQ7 Processing System option that pops up to add the hooks to access the Zynq ARM processor that is physically instantiated in the programable logic of the FPGA.

Once the Zynq processing system IP block appears in the block design, a banner will appear across the top with the option to Run Block Automation. Click on this link and a window will appear specifying the actions of what running block automation will do. In this case, it is applying the board presets for the Arty Z7-20 from the board preset files installed in Vivado back in the first step. Click OK, and wait for the block automation to complete.

Once the block automation for the Zynq processing system has completed, the Arty board peripherals can be quickly added to the block design using the Board tab in the window to the top left of the diagram (as shown below where the other tabs in the window are Sources, Design, and Signals).

Right-click on each desired peripheral you want to add to the block design and select either Auto Connect or Connect Board Component... (which allows a specific choice of IP to connect the peripheral to versus the auto-connect option).

Note that not all peripherals can be added in a single block design as some of them need access to the same package pins on the FPGA, and you cannot drive the same pin with two separate sources (IP blocks in this case) without some sort of multiplexing circuitry (RTL) added.

For a basic starting point, I added the System Clock, 4 LEDs (LD0 - LD3), 2 switches (SW0 - SW1), 4 push buttons (BTN0 - BTN3), 2 RGB LEDs (LD4 - LD5), all of the Arduino shield pins (0 - 41), and the SPI connector (J6). Select the option to run all connection automation that appears and leave the default selects for each in the window that appears detailing the actions running connection automation will execute.

Once everything is connected, use the circle arrow button located on the tool bar along the top of the diagram to regenerate the layout (aka make the block design look pretty and organized). After that, validate the design to verify there are not critical warnings or errors (regular level warnings can be ignored for now). Click the icon of a box with a check mark in it that is also located on the tool bar along the top of the diagram to run validation.

Save and close the block design once successfully validated.

Returning to the Sources tab in the same small window that the Board tab was in, you'll see the block design file towards the top. Right-click on it and select the option to Create HDL Wrapper... This will create the top level Verilog file that instantiates the block design into the project.

Select the option to allow Vivado to manage the wrapper and automatically update it itself.

Allow for Vivado to generate the HDL wrapper and wait until the Updating... text disappears from the upper right-hand corner of the Sources tab.

At this point, the design is complete and ready to be synthesized, place & routed, and to have a bitstream generated for. Synthesis must be ran first, so select Run Synthesis from the Flow Navigator window or press F6.

A window will appear indicating which synthesis runs are about to be launched, in this case, there is only the one synthesis to run so leave the options set to their defaults and click OK. Once successfully completed, a dialog box will appear asking which action to take next. Select the Run Implementation option to place & route the design and click OK. Another window will appear indicating which implementation runs are about to be launched, again leave the options set to their defaults and click OK.

After implementation has successfully completed, another dialog box will appear asking which action to take next. Select the option to generate a bitstream and click OK. Again, leave the leave the options set to their defaults and click OK in the window that appears afterwards indicating which runs are about to launch to generate the bitstream.

Upon successful generation of a bitstream, select the option to open the implemented design and take a look at the end result of the FPGA design for the Arty Z7. The Package tab will give you an overview of what signals are connected to which package pins, and the Device tab will display how much of the programmable logic is used by the design created in the Block Design.

In order to use this hardware design in an embedded application created in Vitis or as the base to an embedded Linux image created with PetaLinux, it needs to be packaged and exported out of Vivado.

Click on the File tab at the top left corner of the Vivado main window and select Export > Export Hardware...

Select the option to include the bitstream in the exported hardware platform and specify the desired output file path. I personally like to use the main project folder for the respective Vivado project. The final screen in the pop-up window will summarize your selections for verification. Click Finish to export the hardware as the Xilinx filetype.XSA

Comments

Please log in or sign up to comment.