I worked as a hardware designer for Intel and others for almost 20 years, working on silicon that powers many of the TOP500 supercomputers. The tools for doing my job sucked!!! Finally enough was enough, and I left Intel to create better ones. And I have. And they will continue to improve. You can use them now at makerchip.com.

WARP-V is a showcase of this revolutionary design methodology and simply the best and most flexible open-source RISC-V model out there. And I created the initial version in a week and a half!

In the summer of 2018, Google sponsored a student, Akos Hadnagy, to formally verify WARP-V using open-source tools, through Google Summer of Code, and Akos has presented his work at one, and soon two, conferences. Likely, another student will be sponsored in 2019. It could be you!

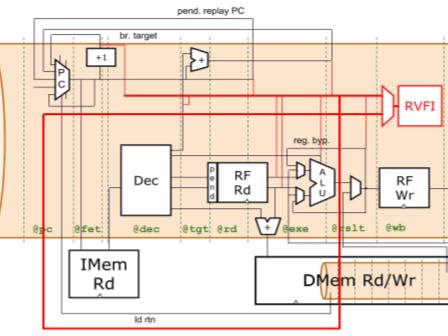

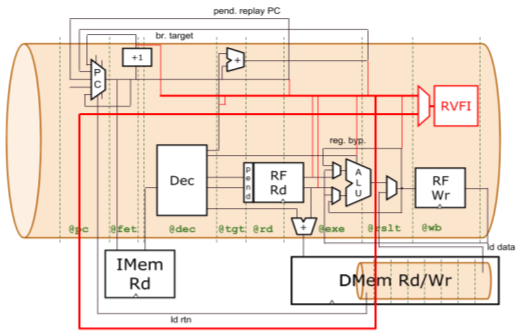

I'm including a teaser image, below. This is a poster that accompanied a presentation I gave at DAC2018. But all you need to know about WARP-V can be found with a quick Google search, or by following this link https://github.com/stevehoover/warp-v.

Interest from academia and industry is building. There are plenty of opportunities to be a part of this next-generation RISC-V design and industry-transforming modeling methodology. Join me in my mission to fix this industry!!!

Cheers,

Steve Hoover (steve.hoover@redwoodeda.com)

Comments

Please log in or sign up to comment.